이전에는 Ubuntu 환경이 필요해서 petalinux 설치가 막혔었다.

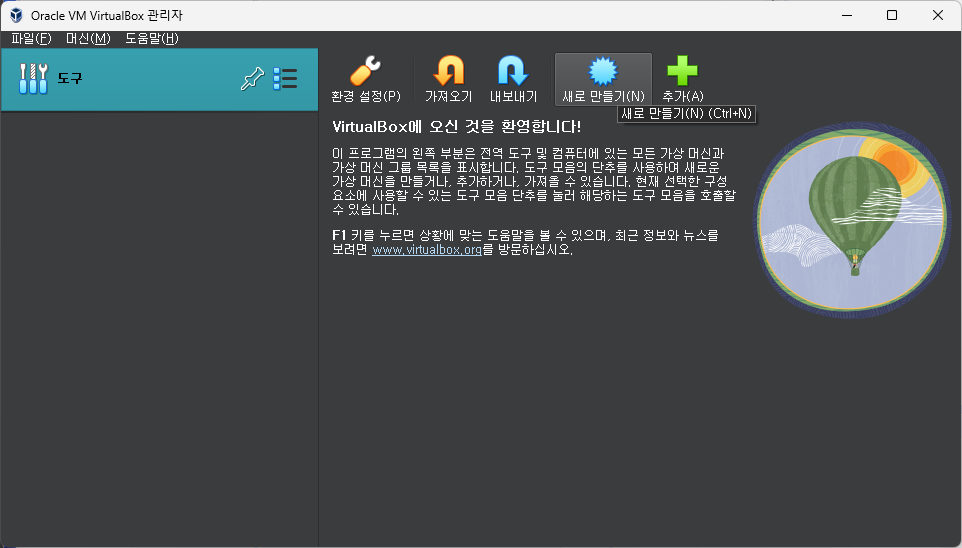

이번 시간에는 Virtualbox를 사용해 Ubuntu를 설치해 본다.

먼저, 다운로드 링크다.

Downloads – Oracle VM VirtualBox

Download VirtualBox Here you will find links to VirtualBox binaries and its source code. VirtualBox binaries By downloading, you agree to the terms and conditions of the respective license. VirtualBox 7.0.14 platform packages The binaries are released unde

www.virtualbox.org

접속해 Windows host 를 받아 설치한다.

* 7.0.14 로 진행하였다.

딱히 건들 것이 없다. Next 만 눌러 설치한다.

설치하게 되면 이런 앱이 켜지게 된다.

우리는 Ubuntu 를 먼저 설치해야 하니 Ubuntu 20.04 LTS 를 다운받으러 간다.(중요 : Petalinux 2018.3을 돌리려면 Ubuntu 16.04 LTS를 받아야 한다)

Ubuntu 20.04.6 LTS (Focal Fossa)

Select an image Ubuntu is distributed on three types of images described below. Desktop image The desktop image allows you to try Ubuntu without changing your computer at all, and at your option to install it permanently later. This type of image is what m

releases.ubuntu.com

Ubuntu 16.04.7 LTS (Xenial Xerus)

Select an image Ubuntu is distributed on two types of images described below. Desktop image The desktop image allows you to try Ubuntu without changing your computer at all, and at your option to install it permanently later. This type of image is what mos

releases.ubuntu.com

64-bit PC desktop image 를 설치해 준다.

설치가 모두 완료되었다면 VM에 우분투를 설치 할 차례이다.

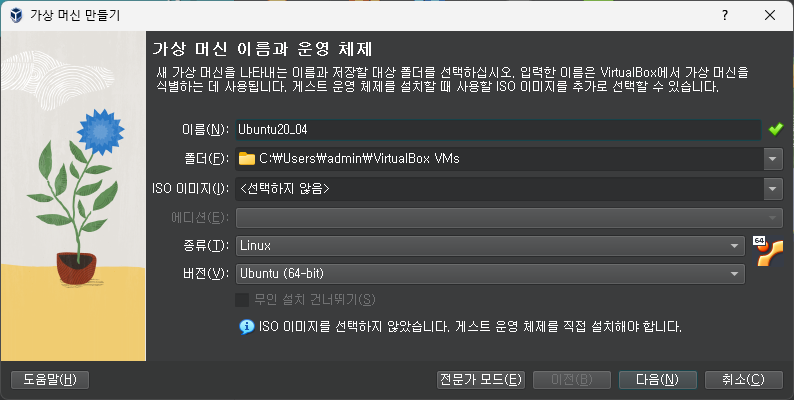

새로 만들기를 선택한다.

이름은 구분할 수 있는 이름으로 설정한다.

메모리와 프로세서의 경우, 자신의 환경에 맞게 설정한다.

Ubuntu 20.04 버전은

- 2 GHz dual core processor

- 4 GiB RAM (system memory)

- 25 GB of hard drive space (or USB stick, memory card or external drive but see LiveCD for an alternative approach)

을 시스템 요구사항으로 말하고 있다.

나는 4 Core, 6GB Memory 로 설정했다.(16.04도 동일)

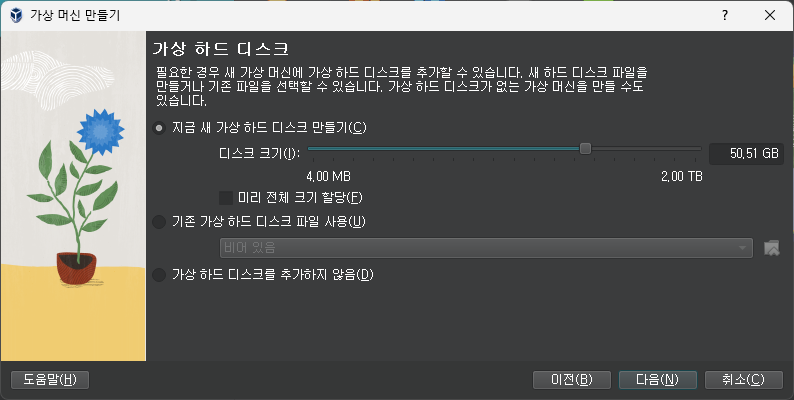

하드 드라이브의 경우, 50기가로 설정했다.(정상적인 동작을 위해 최소 80기가 이상으로 할당하자)

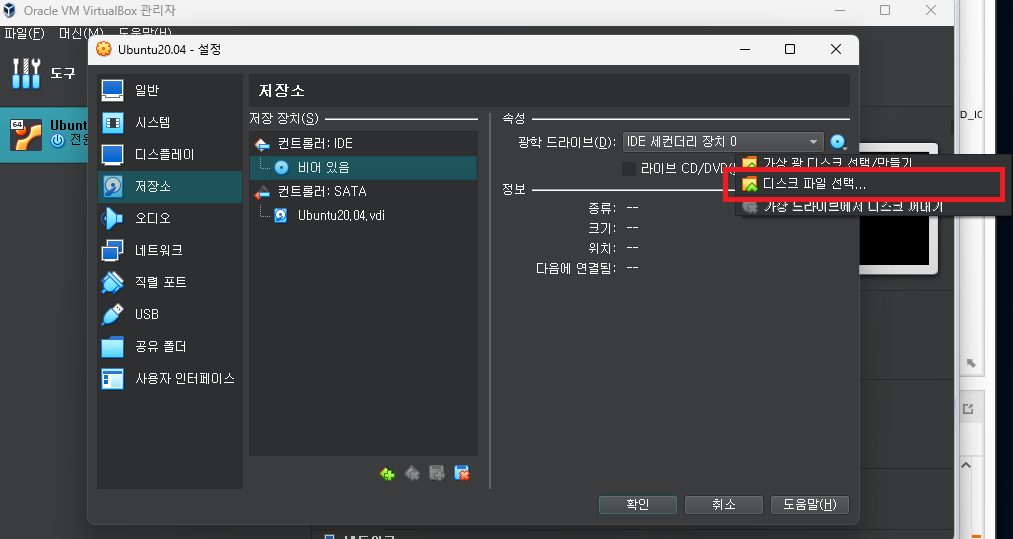

이후 설정에서 저장소 > 디스크 파일 선택 > 다운받은 ubuntu iso 파일 선택을 해 준다.

확인을 누르고, 실행시켜준다.

그러면 알아서 실행이 되고, 우분투를 설치 할 건지에 대해 물어본다.

언어는 영어로 놓고 Install Ubuntu 를 클릭한다.

Keyboard layout 도 English(US) 로 설정해 준다.

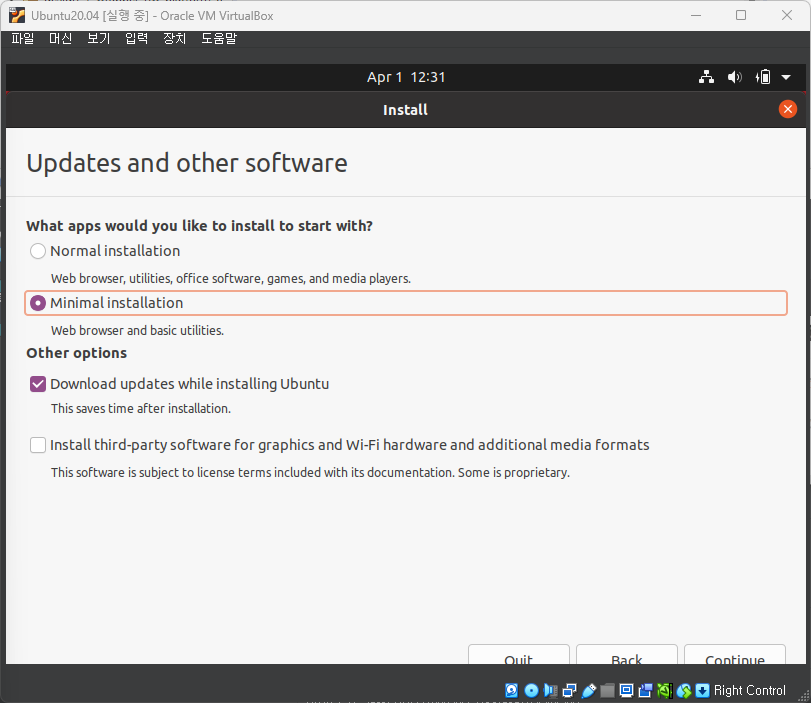

Minimal installation 을 클릭하고 Continue (16.04 버전은 이런게 없다)

Erase disk and install Ubunu 누르고 Install Now 클릭

Continue 클릭 해 준다.

위치를 물어보는 것은 시간대 때문에 그렇다. 아무거나 해도 상관 없다.

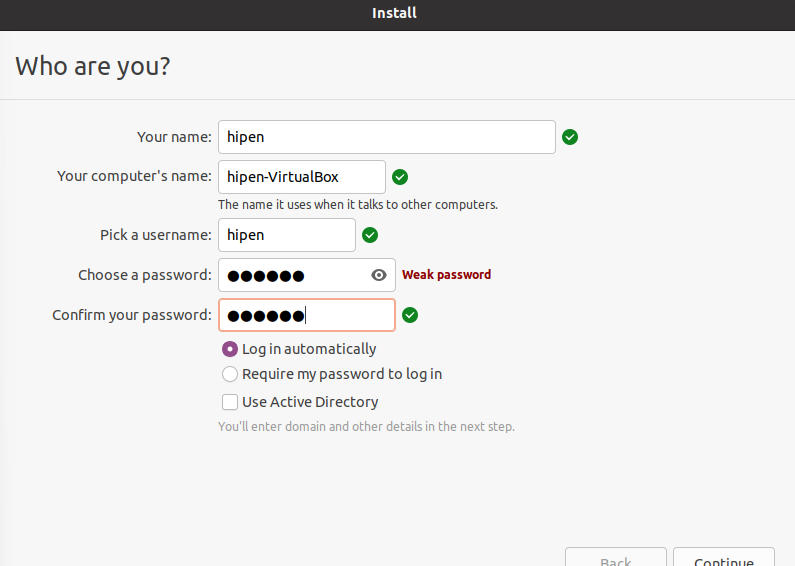

name, password 를 정하고 continue 를 눌러준다.

간단한 용도로만 쓸 예정이기 때문에 보안은 크게 신경 쓰지 않는다.

설치에 시간이 어느 정도 소요되기 때문에 기다려 준다.

설치가 끝나면 재시작 해 준다.

(이후 내용은 시행착오이니 보드로 petalinux 돌리기 - [3] 의 16.04 설치 내용부터 보면 깔끔하게 설치 가능하다)

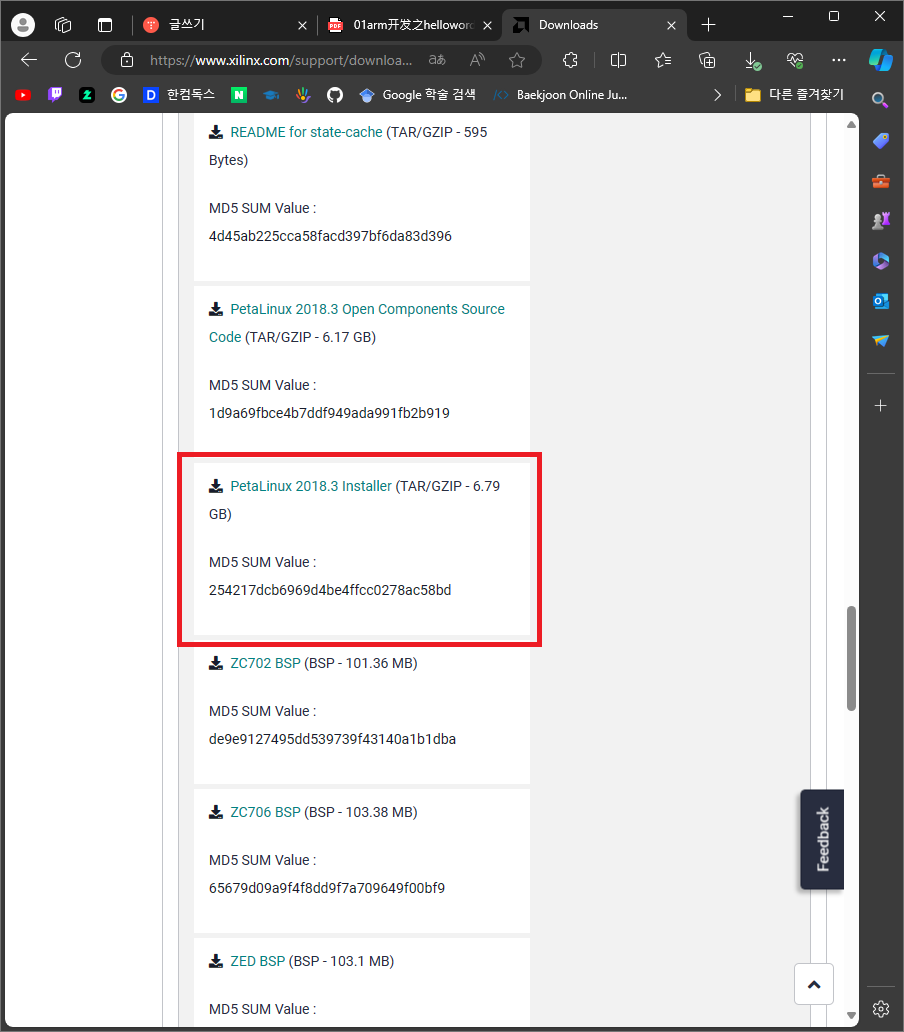

Firefox 브라우저를 통해 다시 petalinux 2018.3 을 다운받는다.

다음으로 리눅스 콘솔을 열어 다음과 같은 명령을 실행한다. (바탕화면에서 우클릭으로 열 수 있다.)

sudo apt-get install update

sudo apt-get install -y tofrodos iproute2 gawk gcc g++ git make net-tools libncurses5-dev tftpd-hpa zlib1g:i386 libssl-dev flex bison libselinux1 gnupg wget diffstat chrpath socat xterm autoconf libtool tar unzip texinfo zlib1g-dev gcc-multilib build-essential libsdl1.2-dev libglib2.0 screen pax gzip automake

sudo 명령어로 인해 Password 를 요구하는데, 버튼을 눌러도 아무 반응이 없다.

하지만 걱정하지 말자. 실제로는 비밀번호가 다 쳐지고 있으니까 마음 놓고 pw 를 입력하면 된다.

.. 로 될 줄 알았는데 Python 이 발목을 잡았다.

$ sudo apt install python 으로 설치를 했는데, 자꾸 2.7.3 보다 위의 버전을 설치해 오라고 했다.

리눅스 우분투 python 다른 버전 설치

작업 환경 - OS : Ubuntu 18.04.6 LTS 기본적으로 우분투 운영체제에 python2, pytho3가 설치되어있었다. 하지만 내가 개발한 것을 리눅스 서버에서 돌리려면 아무래도 개발환경과 같은 버전으로 맞춰주는

joytk.tistory.com

따라서 이 포스트를 참고해 파이썬 2.7.3을 설치했다.

근데도 계속 다른 파이썬 버전이 잡히는 것 같다.

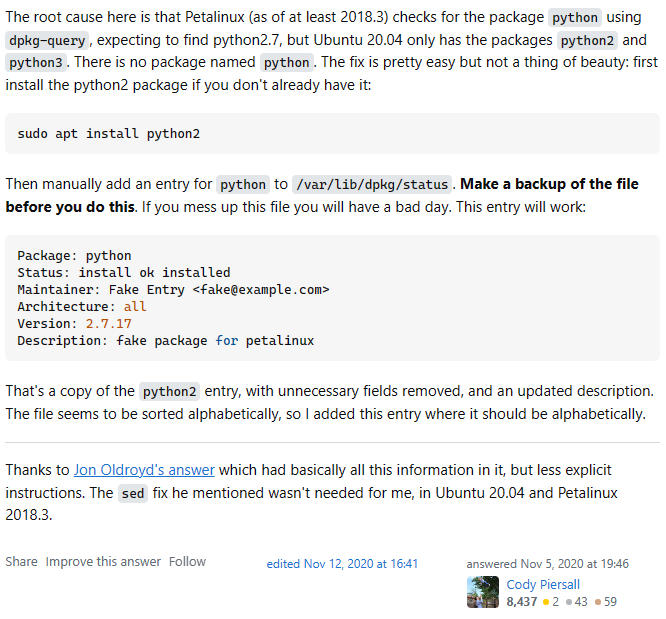

찾아보니 같은 이슈를 겪고 있는 외국인이 많은 것 같다.

python error when installing Xilinx Petalinux on Ubuntu 20.04

I got this error while I tried to install Xilinx Petalinux on Ubuntu 20.04 dpkg-query: package 'python' is not installed and no information is available Use dpkg --info (= dpkg-deb --info) to exam...

stackoverflow.com

Cody Piersall 씨가 준 설치법을 참고로 하면 실행이 된다.

내용은 다음과 같다.

다음은 다운로드가 모두 끝난 petalinux 파일을 를 옮겨준다.

나는 Downloads --> /home/<사용자명>/peta2018 폴더에 저장했다.

파일 실행을 위해 chmod 로 실행 파일의 권한을 바꿔준다. 이후 실행까지 한다.

chmod 777 petalinux-v2018.3-final-installer.run

./petalinux-v2018.3-final-installer.run

진행이 되면서 EULA 등 license agreements 가 나오는데,

pgdn 키를 이용해서 아래로 내려서 볼 수도 있고, q를 누르면 즉시 뷰어가 꺼진다.

그리고 모든 항목에 y 를 눌러 계속 설치하자.

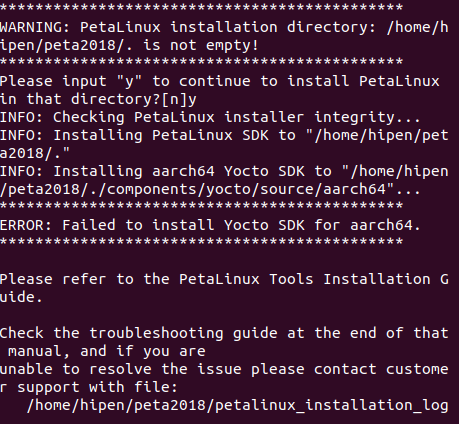

Yocto SDK 에러가 났다..

dpkg 때문에 python 이 인식이 안되서 에러가 난다니 하는 사람들도 있었다.

일단 보류..

다른 PC 환경에서도 진행 해 보았다.

$ sudo apt upgrade 를 먼저 진행하고

Python 설치부터 python2 를 설치해 보았다.

그리고 메뉴얼 방식으로 /var/lib/dpkg/status 파일을 수정했다.

$ sudo vi /var/lib/dpkg/status

Package: python

Status: install ok installed

Maintainer: Fake Entry <fake@example.com>

Architecture: all

Version: 2.7.17

Description: fake package for petalinux

의 내용을 가장 상단에 추가해 줬다.

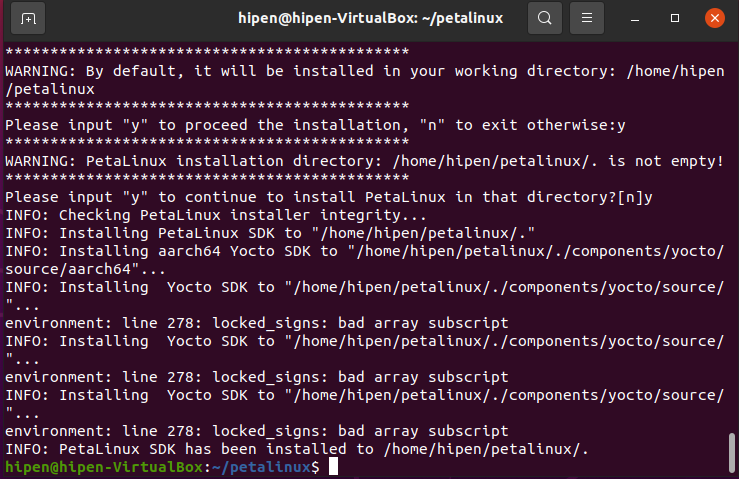

$ sudo apt upgrade 이후

재부팅을 한 번 하고 다시 진행해 보았다.

qemu 설치

$ sudo apt install python-dev

파이썬 버전이 역시 문제인 것 같다.

에러가 좀 뜨긴 하는데 설치는 완료되었다고 뜬다.

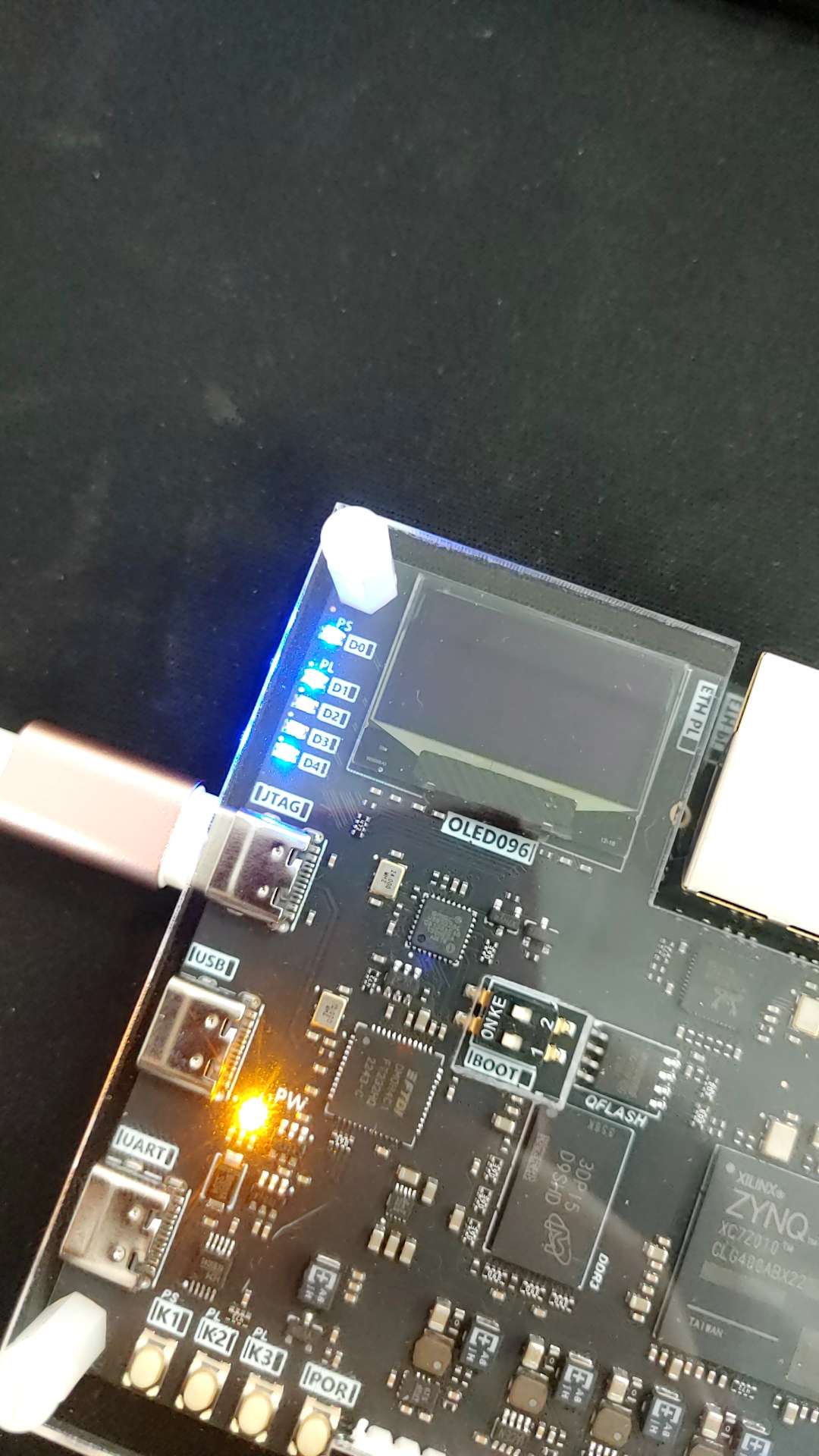

'ZYNQ_MINI' 카테고리의 다른 글

| [ZYNQ MINI] PWM 예제, Simulation 써 보기 (0) | 2024.04.12 |

|---|---|

| [ZYNQ MINI] 보드로 petalinux 돌려보기 - [3] (3) | 2024.04.03 |

| [ZYNQ MINI] 보드로 petalinux 돌려보기 - [1] (0) | 2024.04.01 |

| [ZYNQ MINI] SDK를 사용해 코드 내장시키기 (0) | 2024.04.01 |

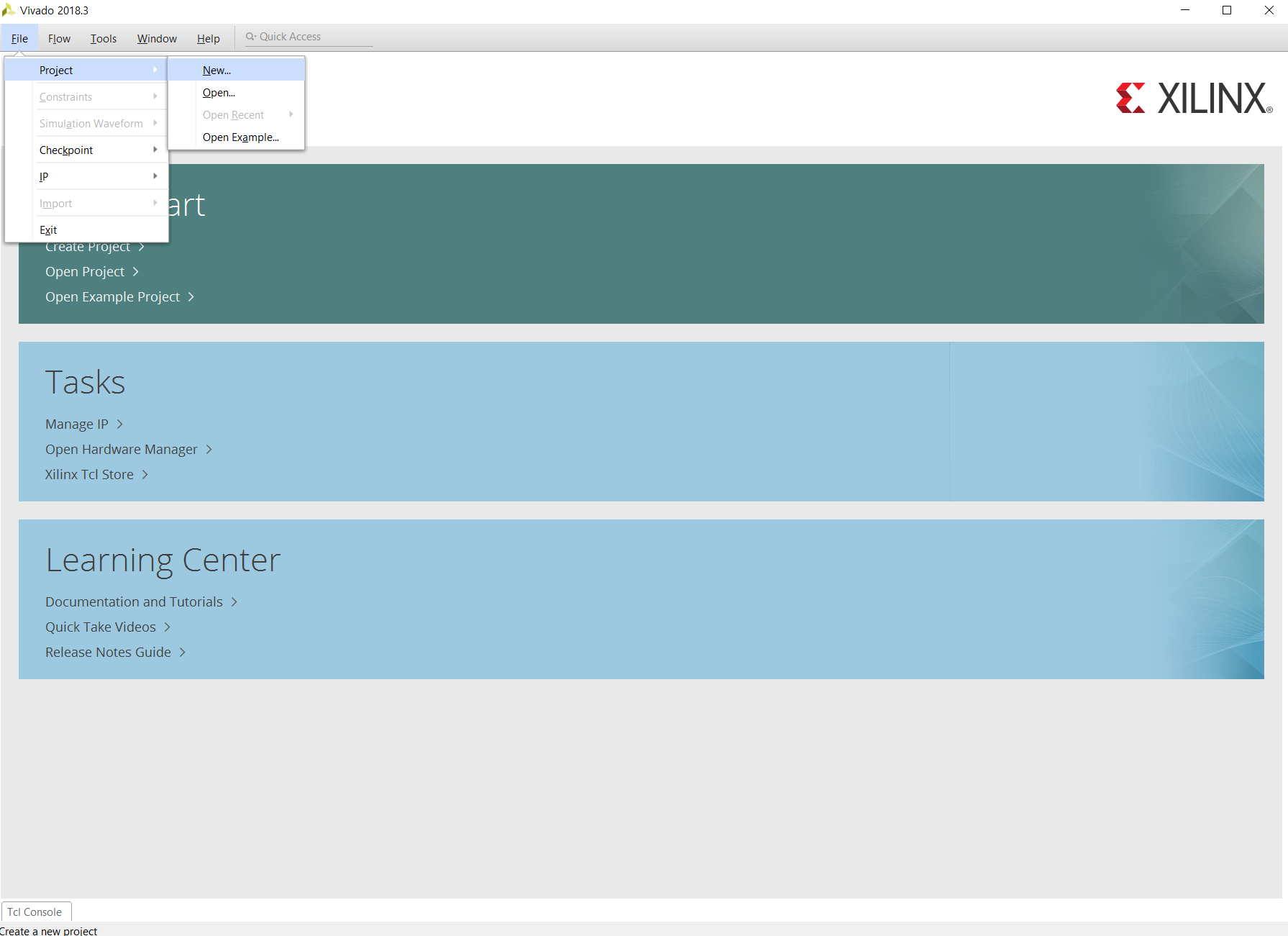

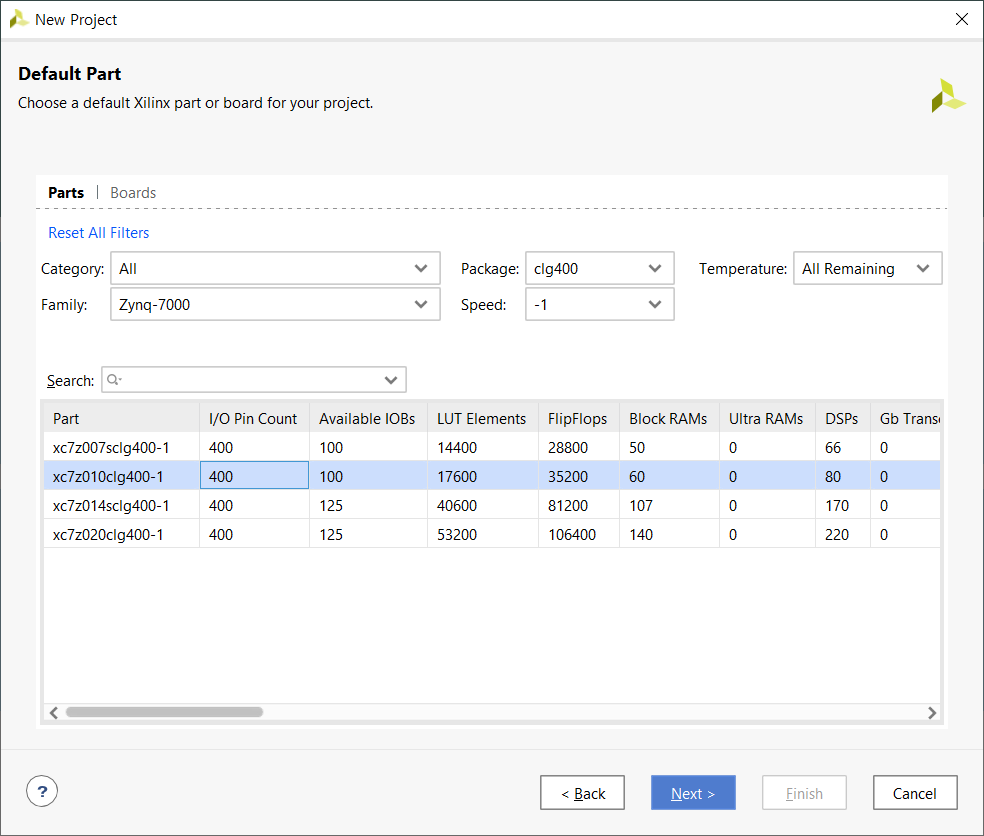

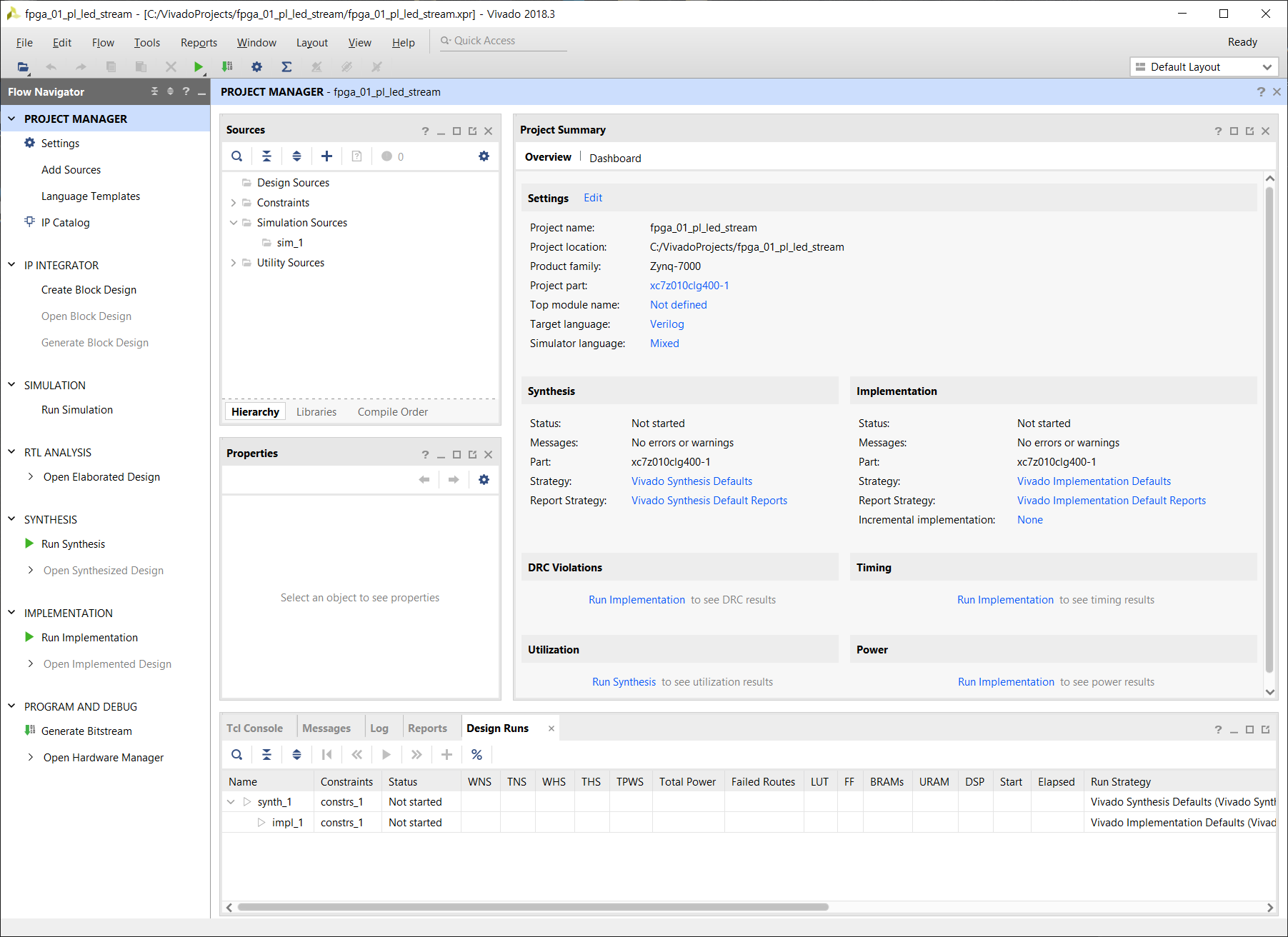

| [ZYNQ MINI] Vivado로 첫 프로젝트 생성 (0) | 2024.04.01 |