03_Use SDK to solidfy FLASH code.pdf 를 참고하였다.

이번에는 셀러가 제공해 준 코드를 사용해 만들어 보도록 한다.

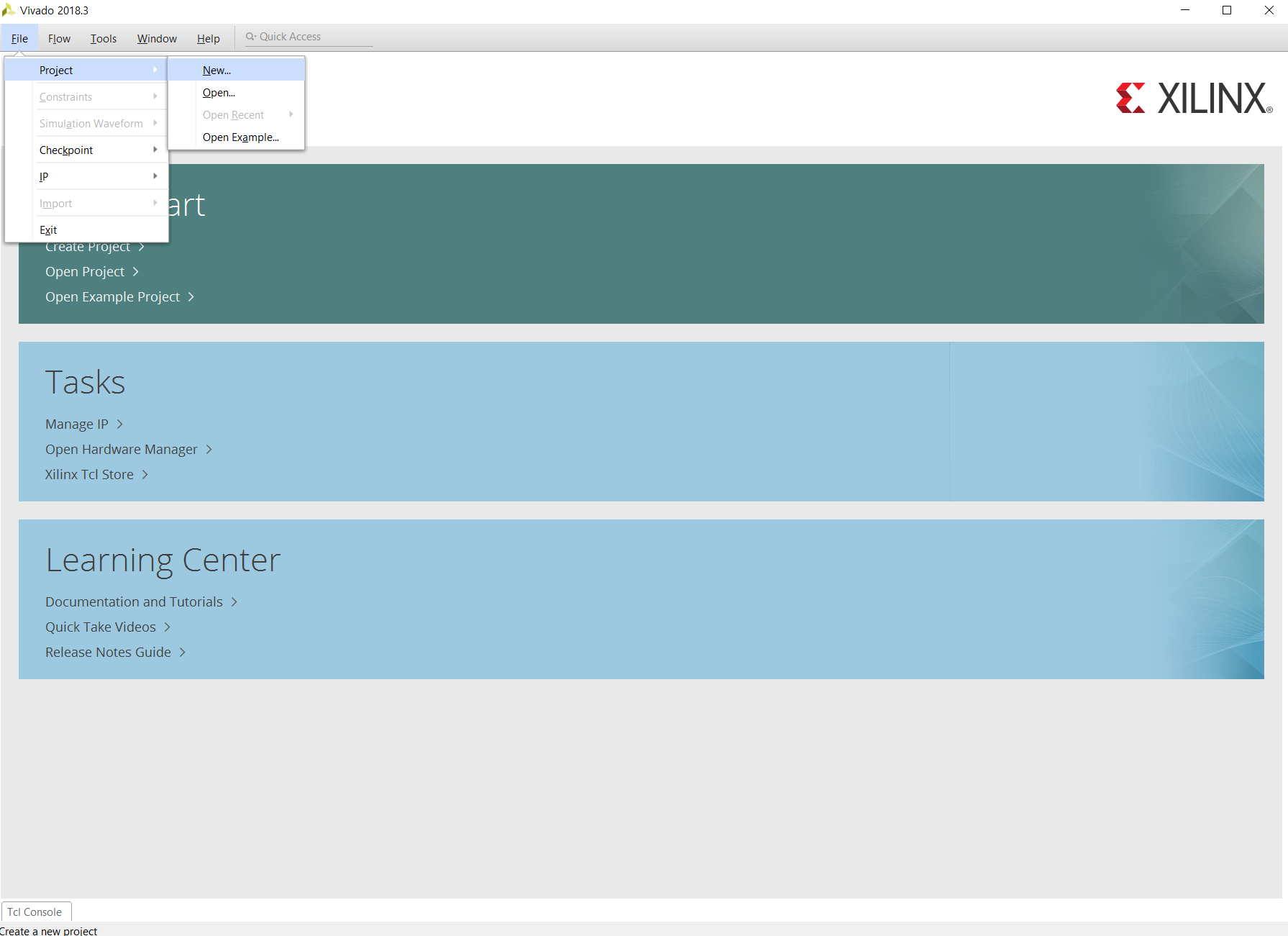

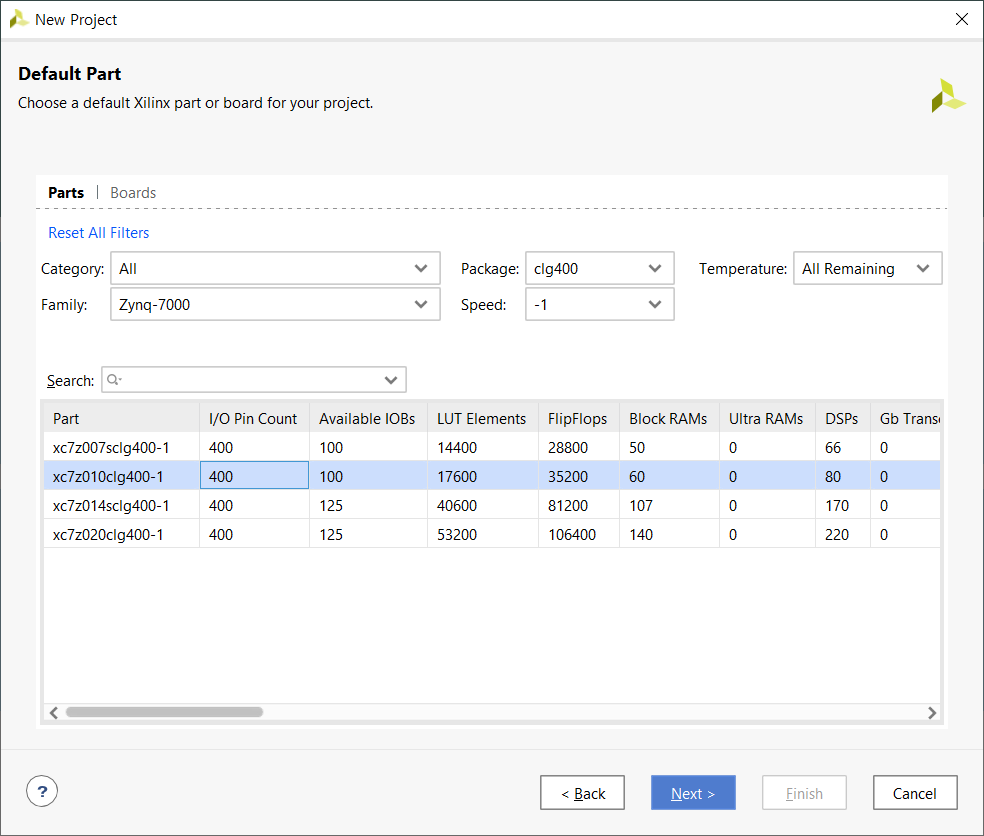

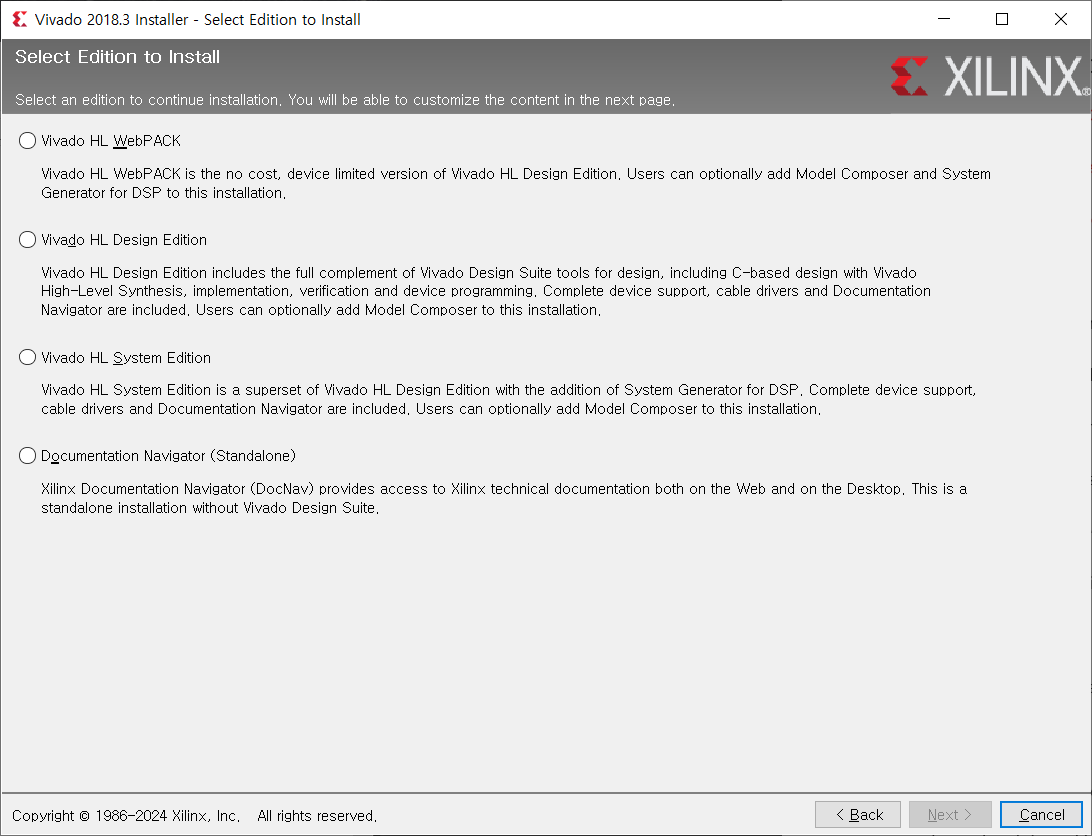

먼저, 프로젝트를 하나 생성한다.

| 프로젝트 네임 | fpga_03_fpga_flash_download |

| 프로젝트 타입 | RTL project |

| 소스 추가 | X |

| 보드 설정 | xc7z010clg400-1 |

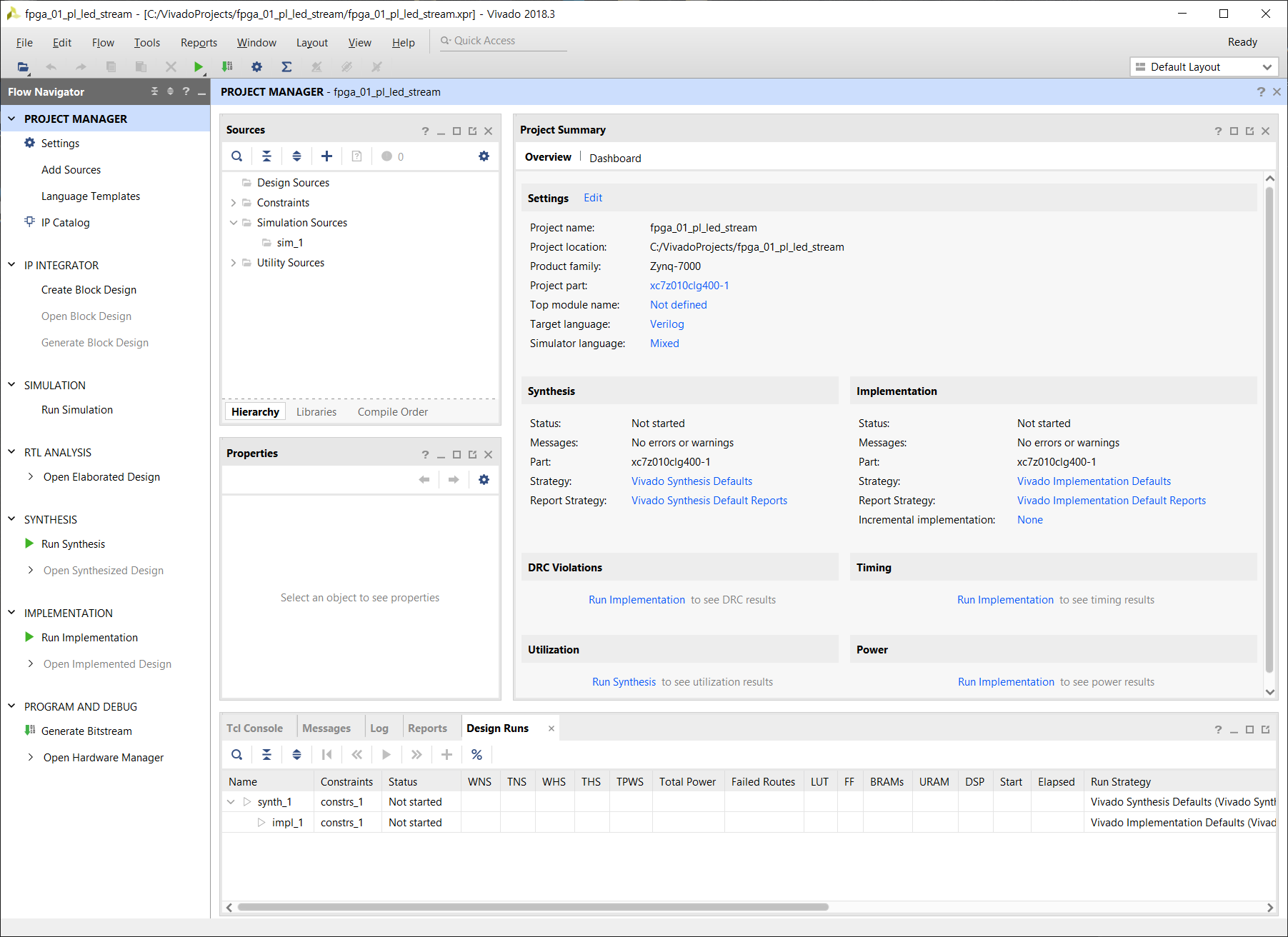

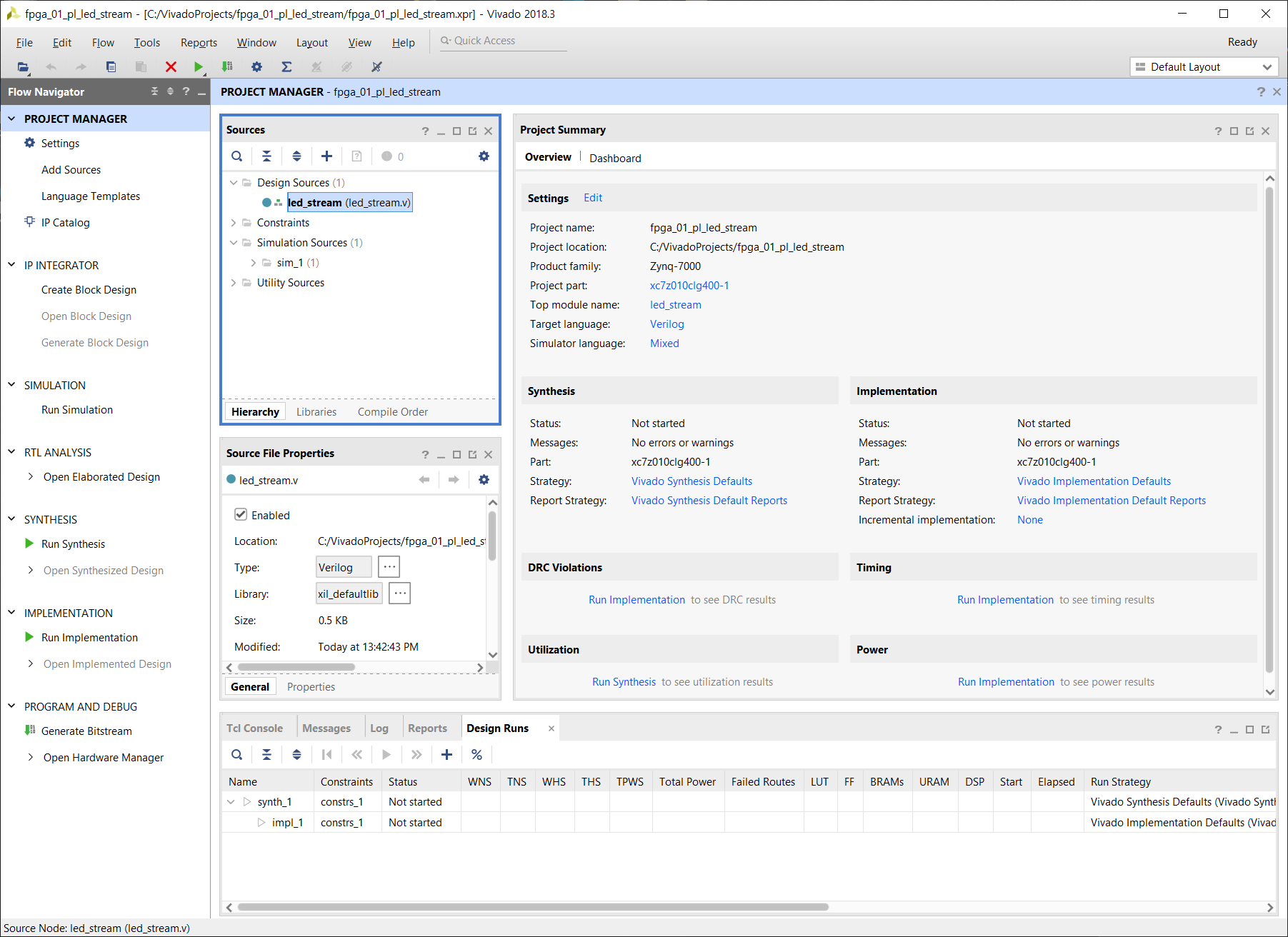

생성된 프로젝트 모습이다.

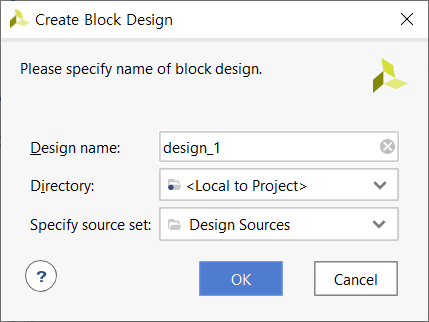

여기서 이번에는, IP INTEGRATOR 의 Generate Block Design 을 선택한다.

OK 를 선택한다.

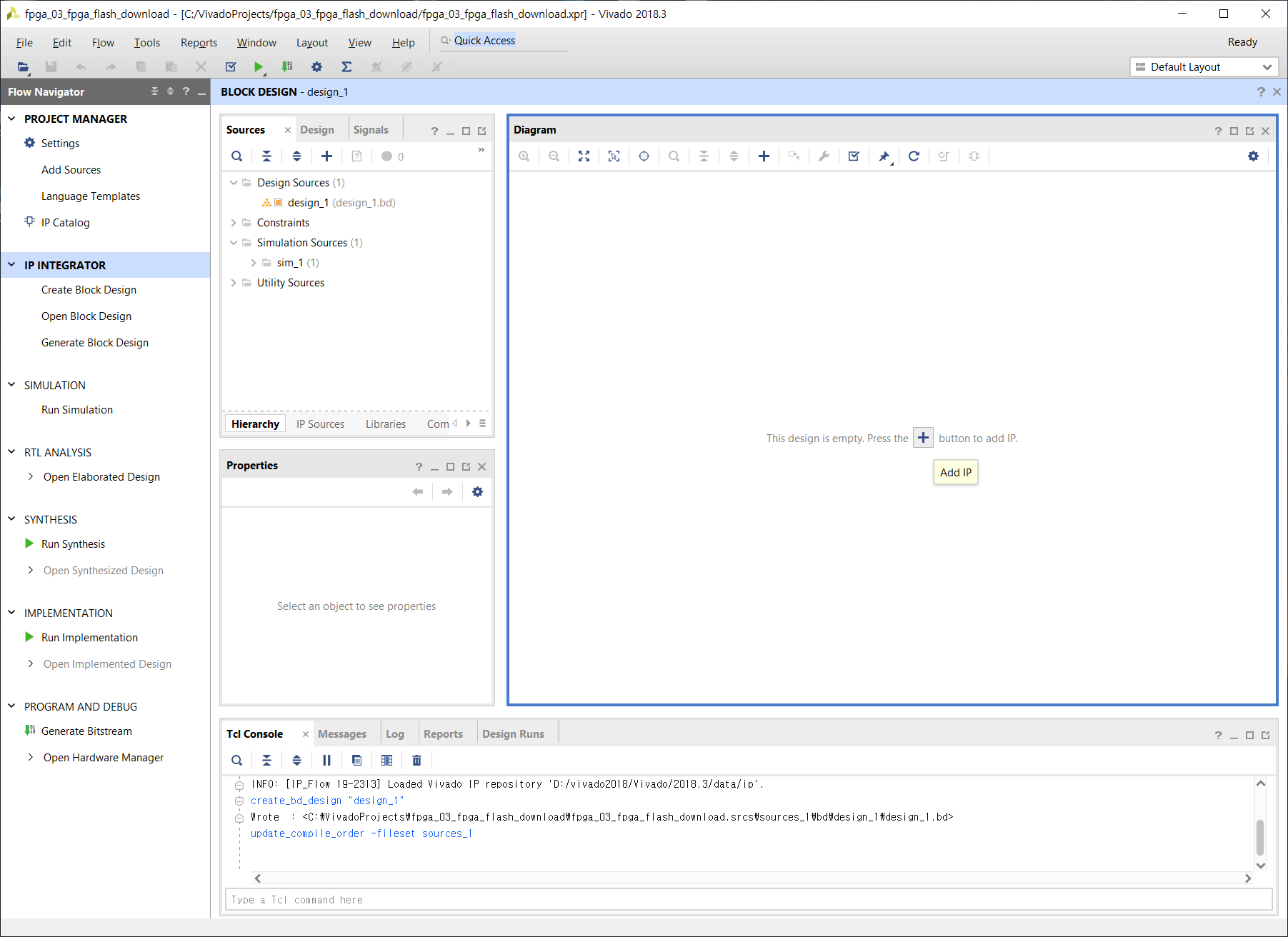

그럼 Design 탭이 추가로 생성된 것을 볼 수 있다.

소스에도 디자인 소스에 design_1.bd 파일이 추가된 것을 볼 수 있다.

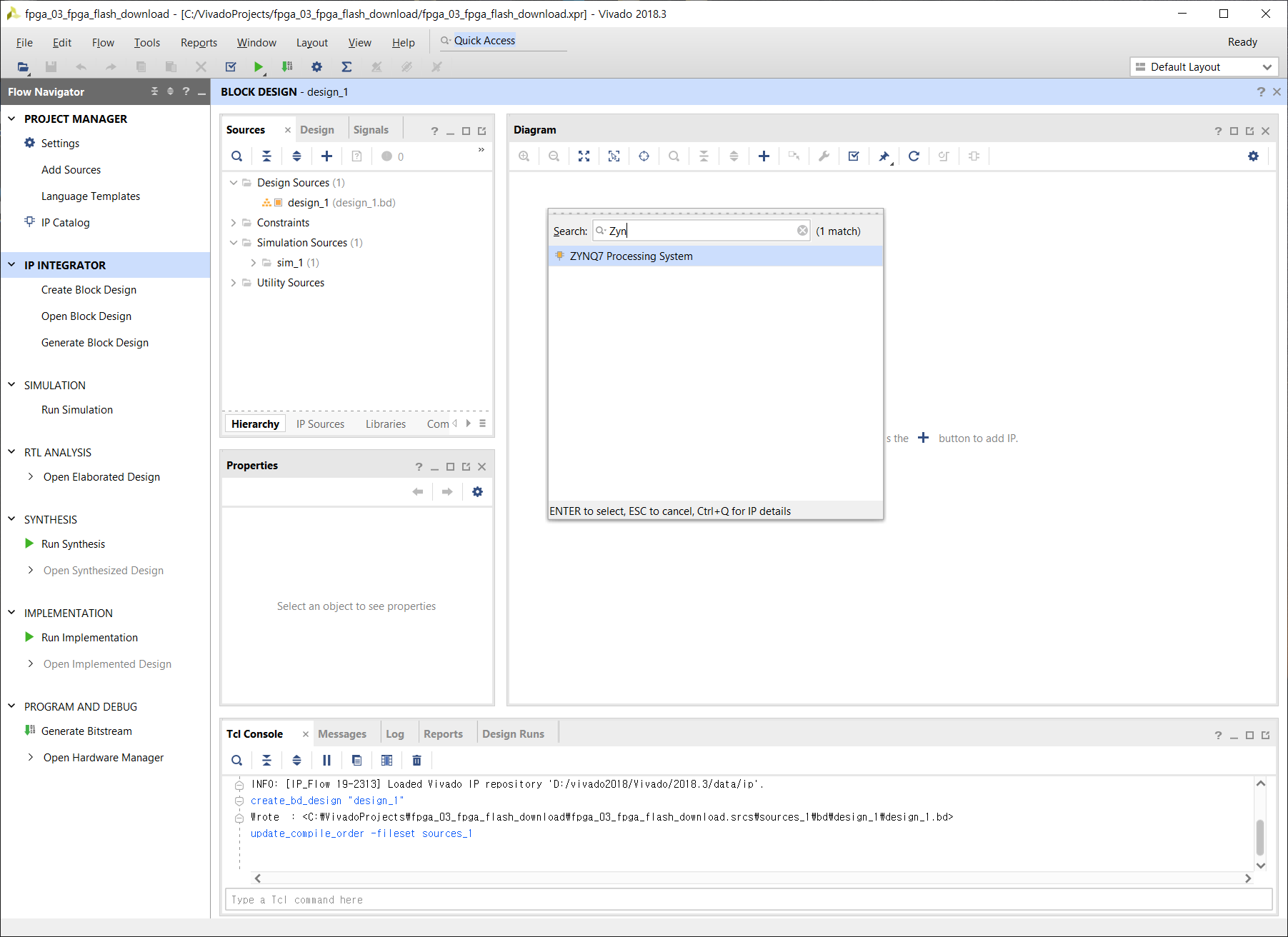

다이어그램에 + 에 커서를 갖다대면 Add IP 라는 창이 뜨는데, 이를 선택한다.

ZYNQ7 Processing System 을 선택한다.

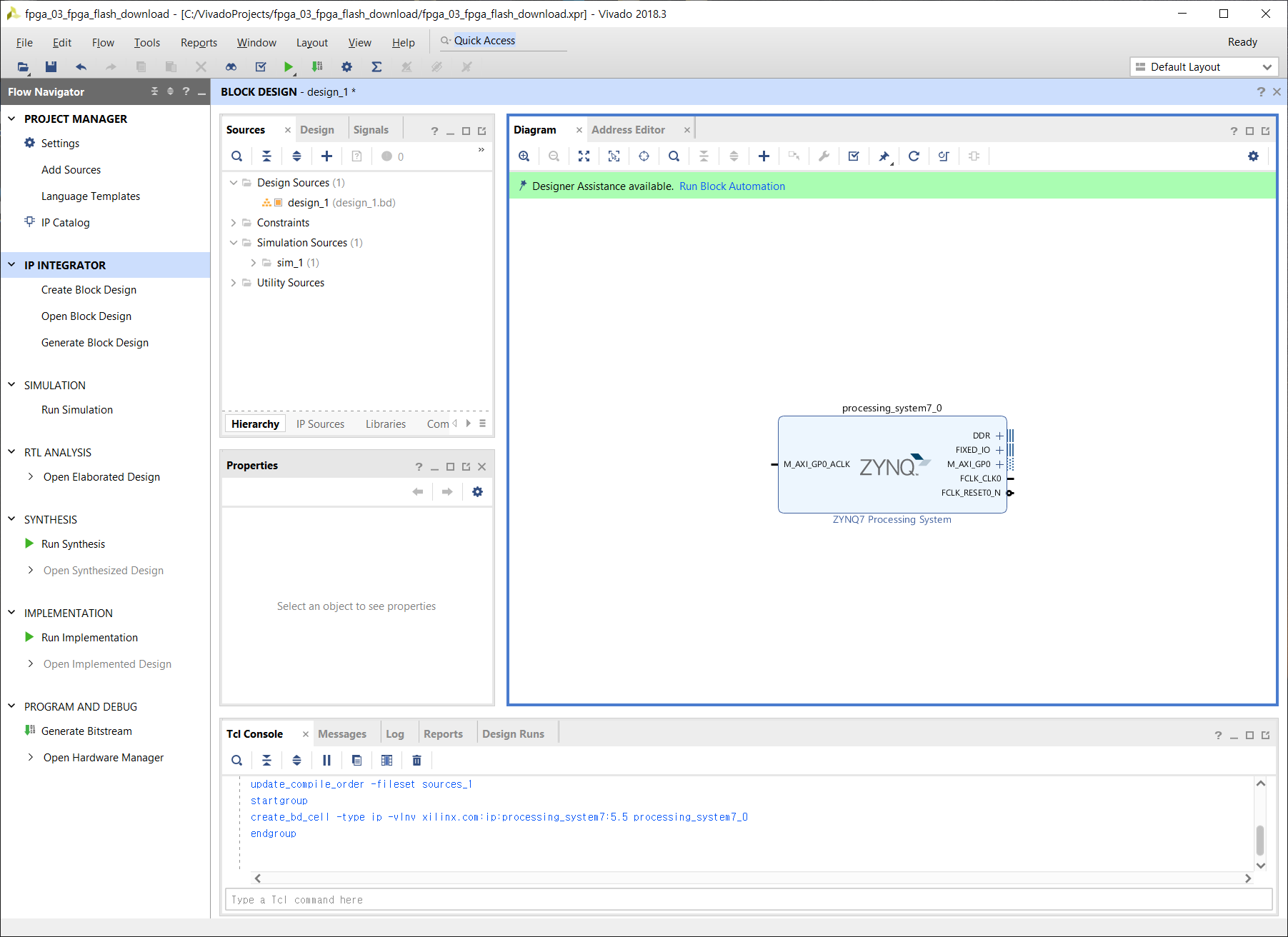

그러면 ZYNQ7 PS 를 가지고 오게 된다. 이를 더블클릭 해 보자.

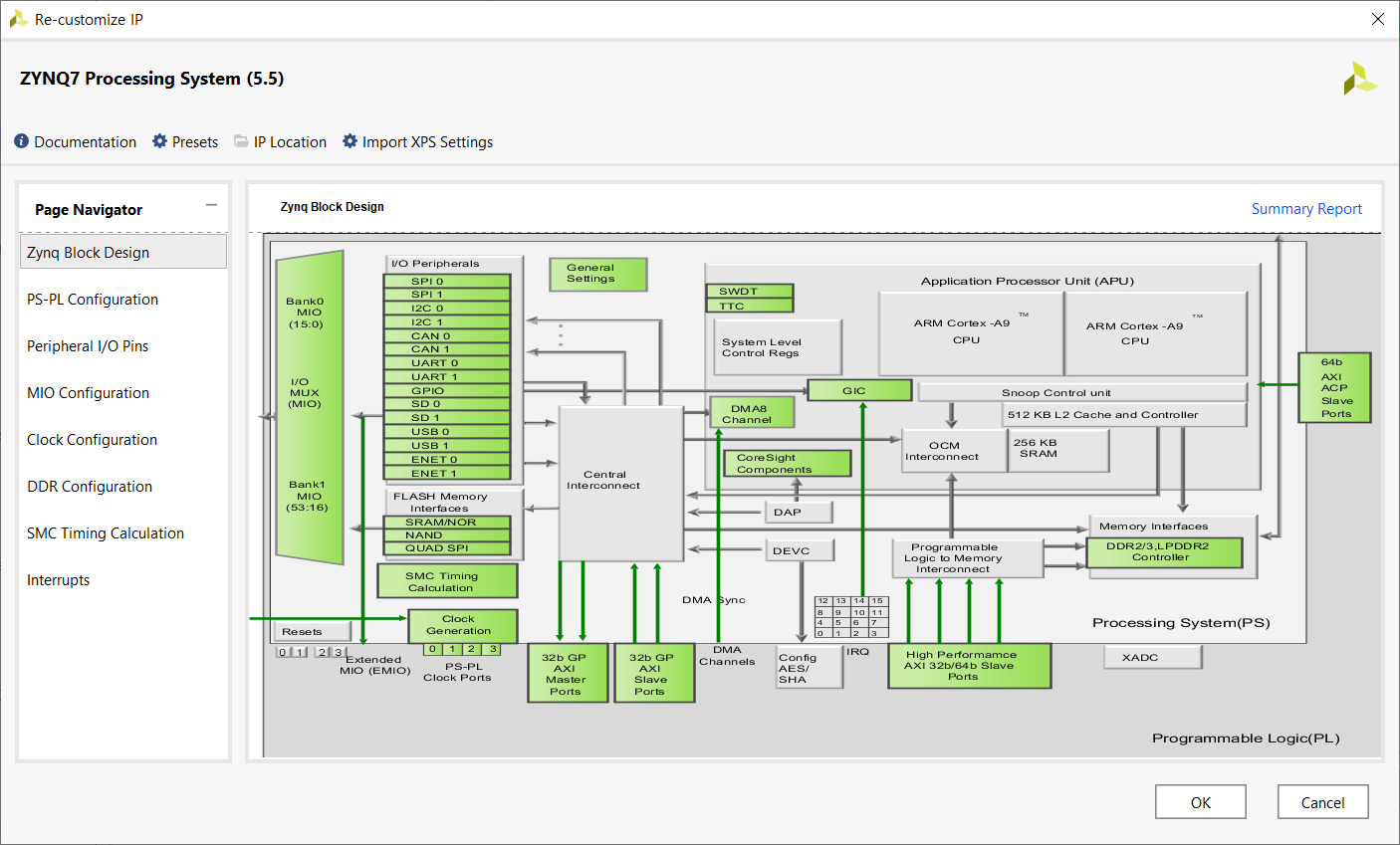

내부 구조가 나오게 된다.

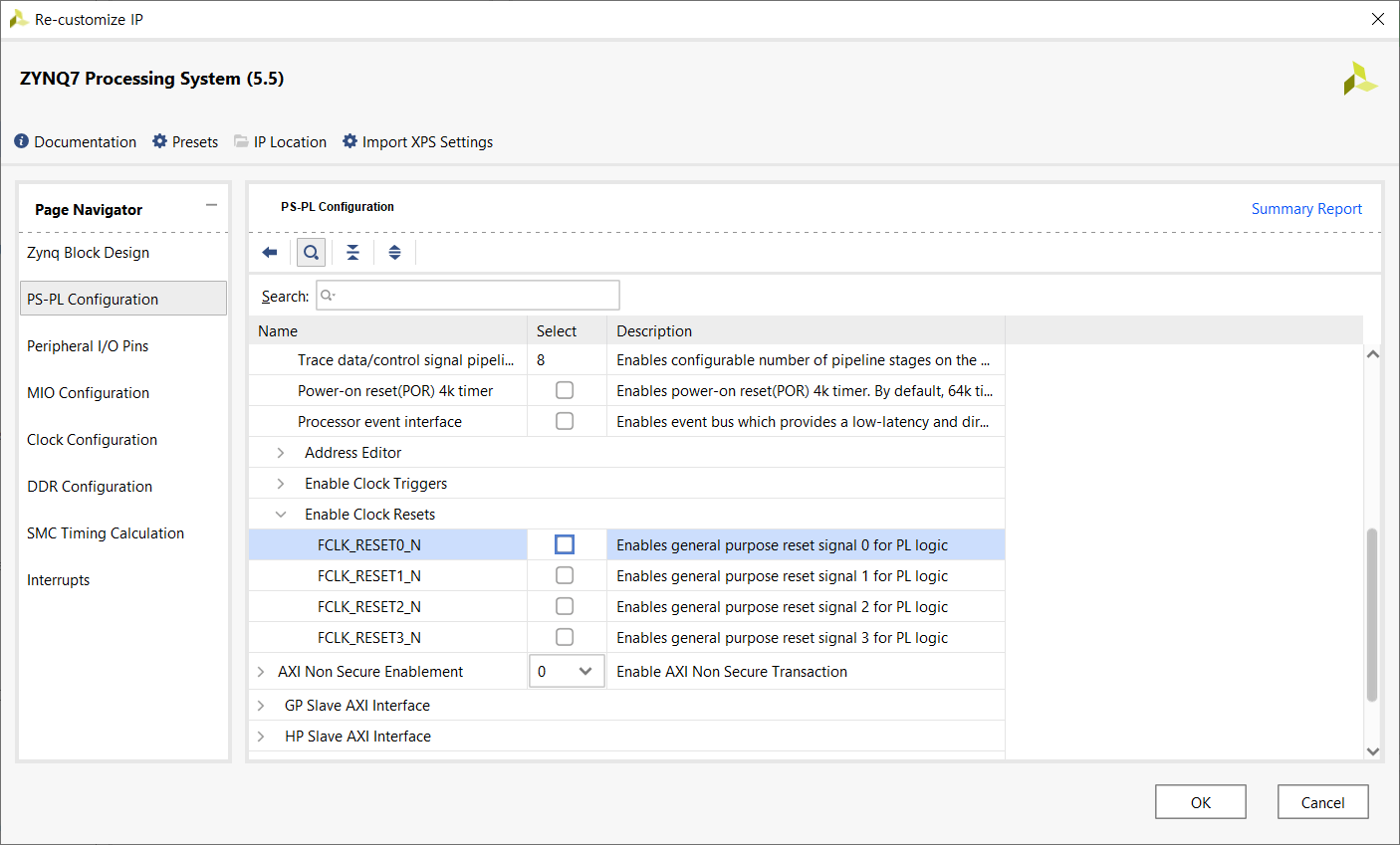

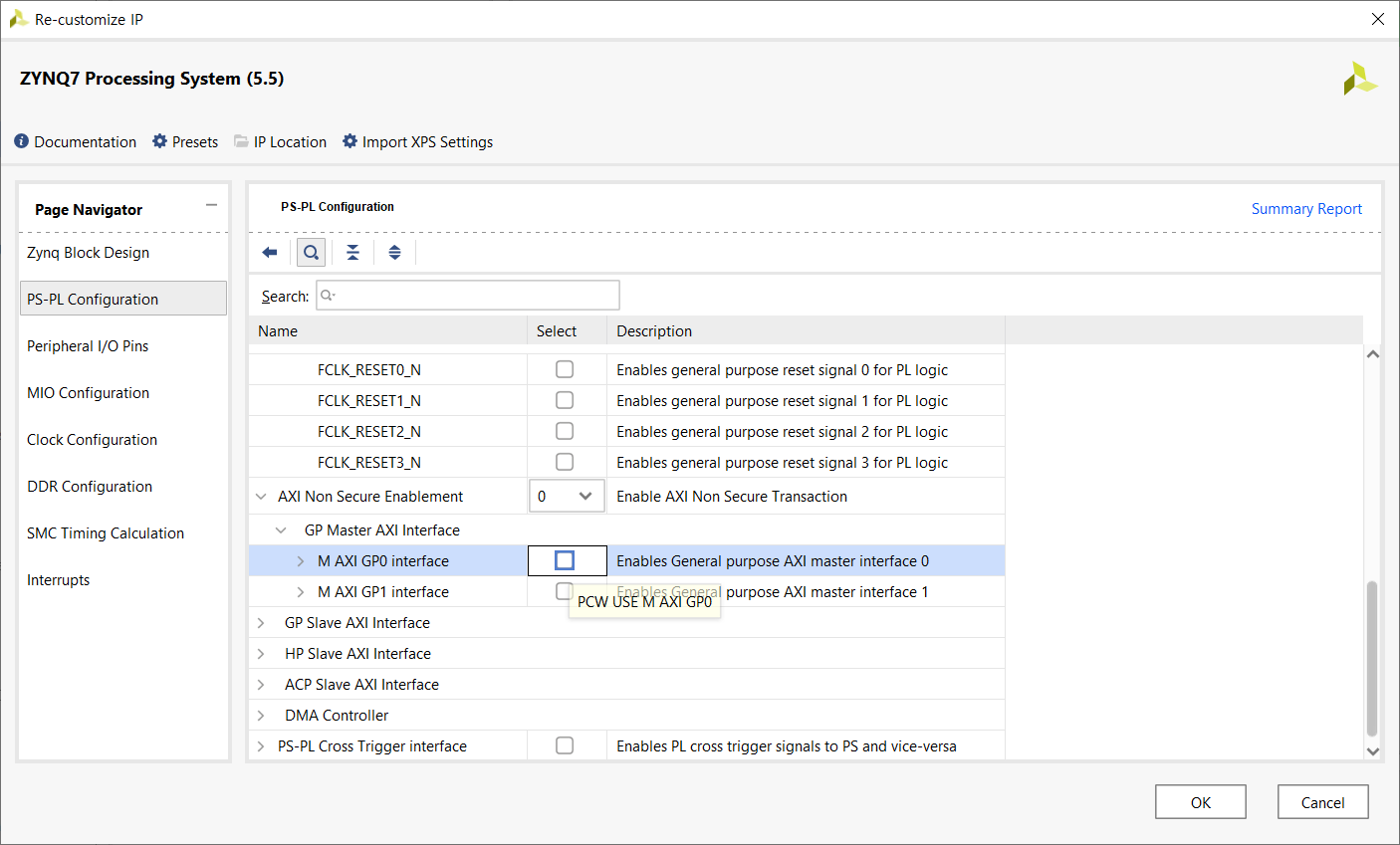

이번에 설정할 것은, PS-PL Configuration 을 먼저 클릭해 보자.

General > Enable Clock Resets > FCLK_RESET0_N 의 Select 를 disable 한다.

아래의 AXI Non Secure Enablement > GP Master AXI Interface > M AXI GP0 interface의 select 도 disable 한다.

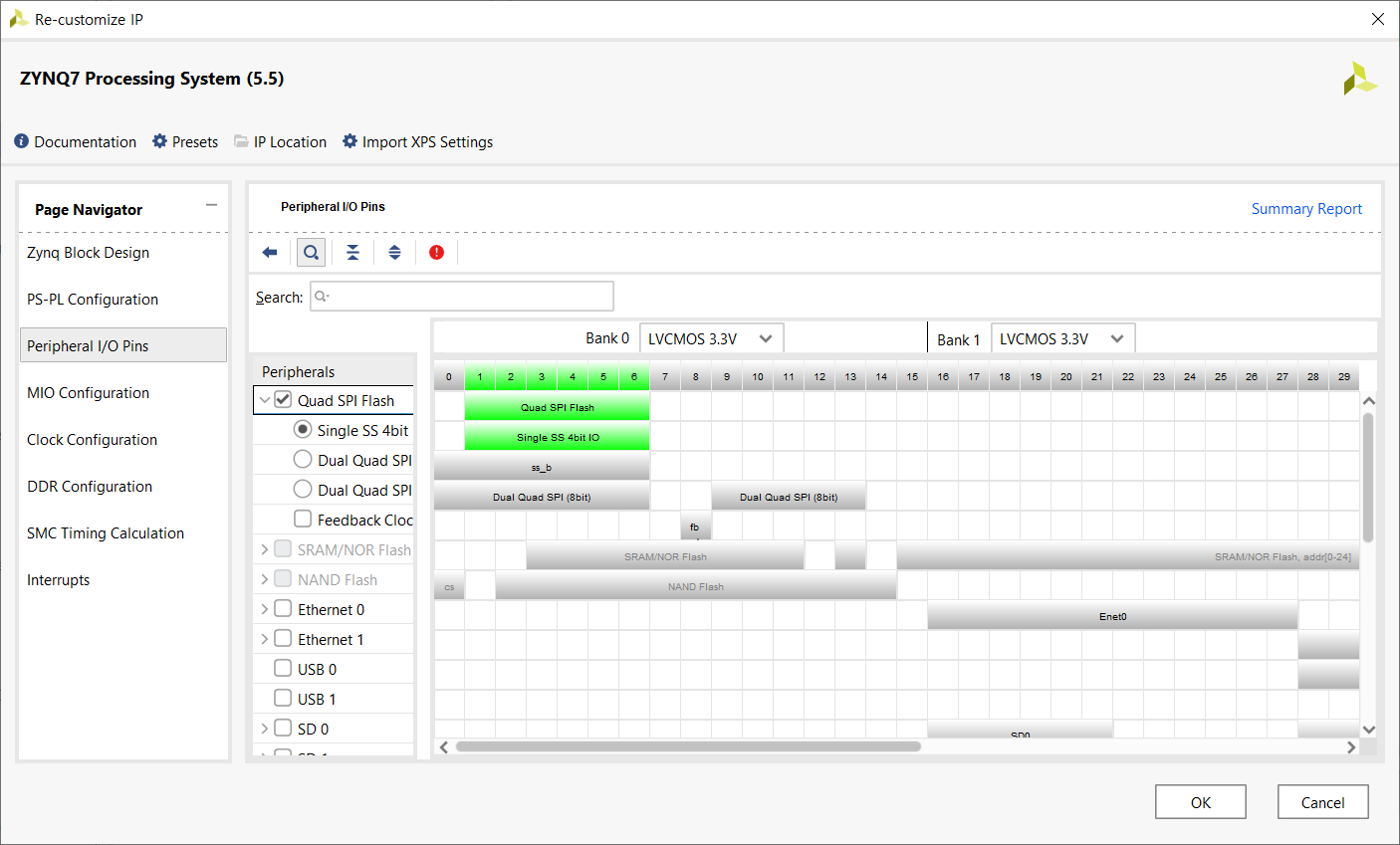

왼쪽 네비게이터 탭의 Peripheral I/O Pins 에 들어간다.

Quad SPI Flash 를 활성화 한다.

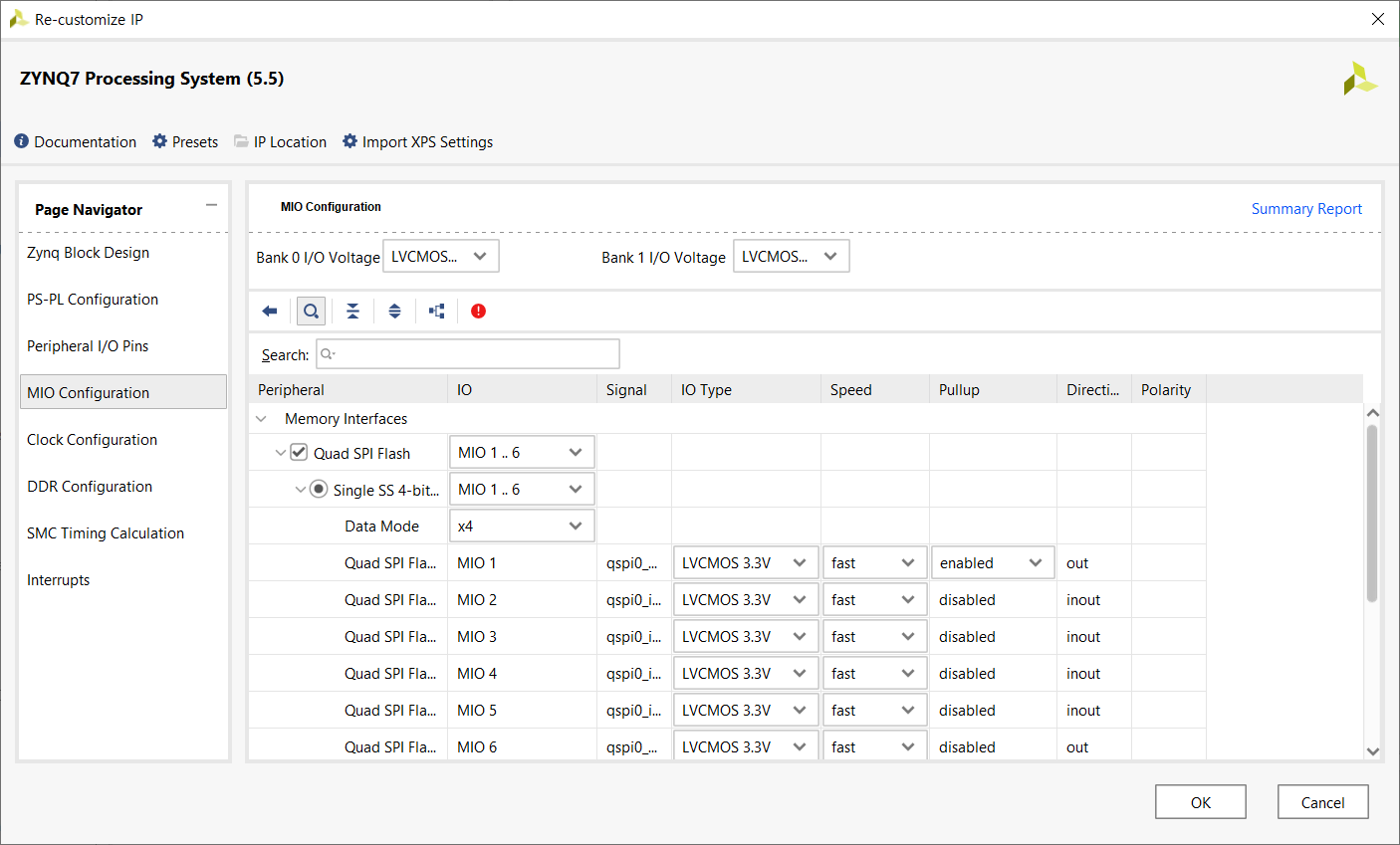

이후 MIO Configuration 으로 들어가 Quad SPI Flash 항목의 Speed를 모두 Fast로 바꾼다.

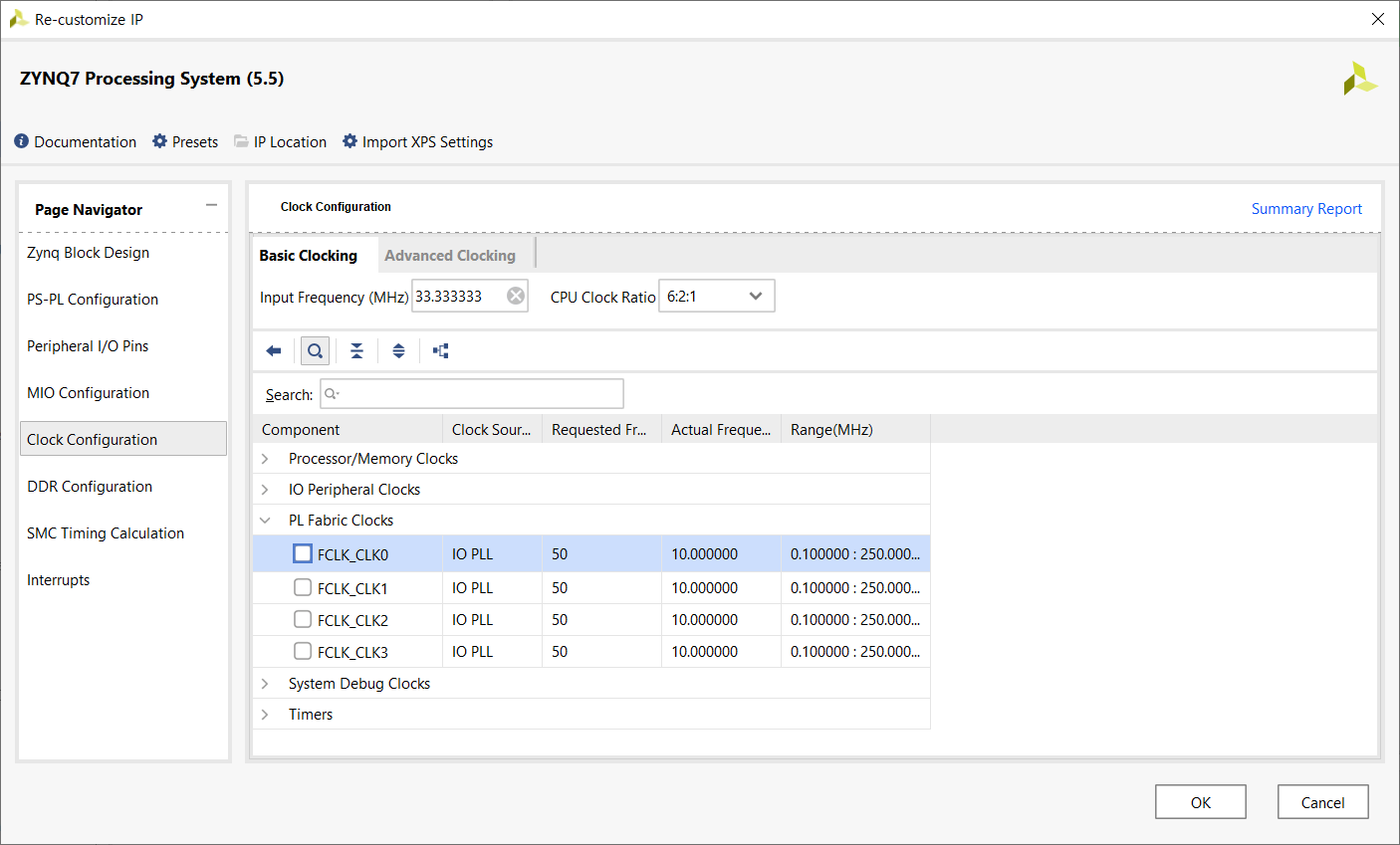

이후 Clock Configuration > PL Fabric Clocks > FCLK_CLK0 을 disable 한다.

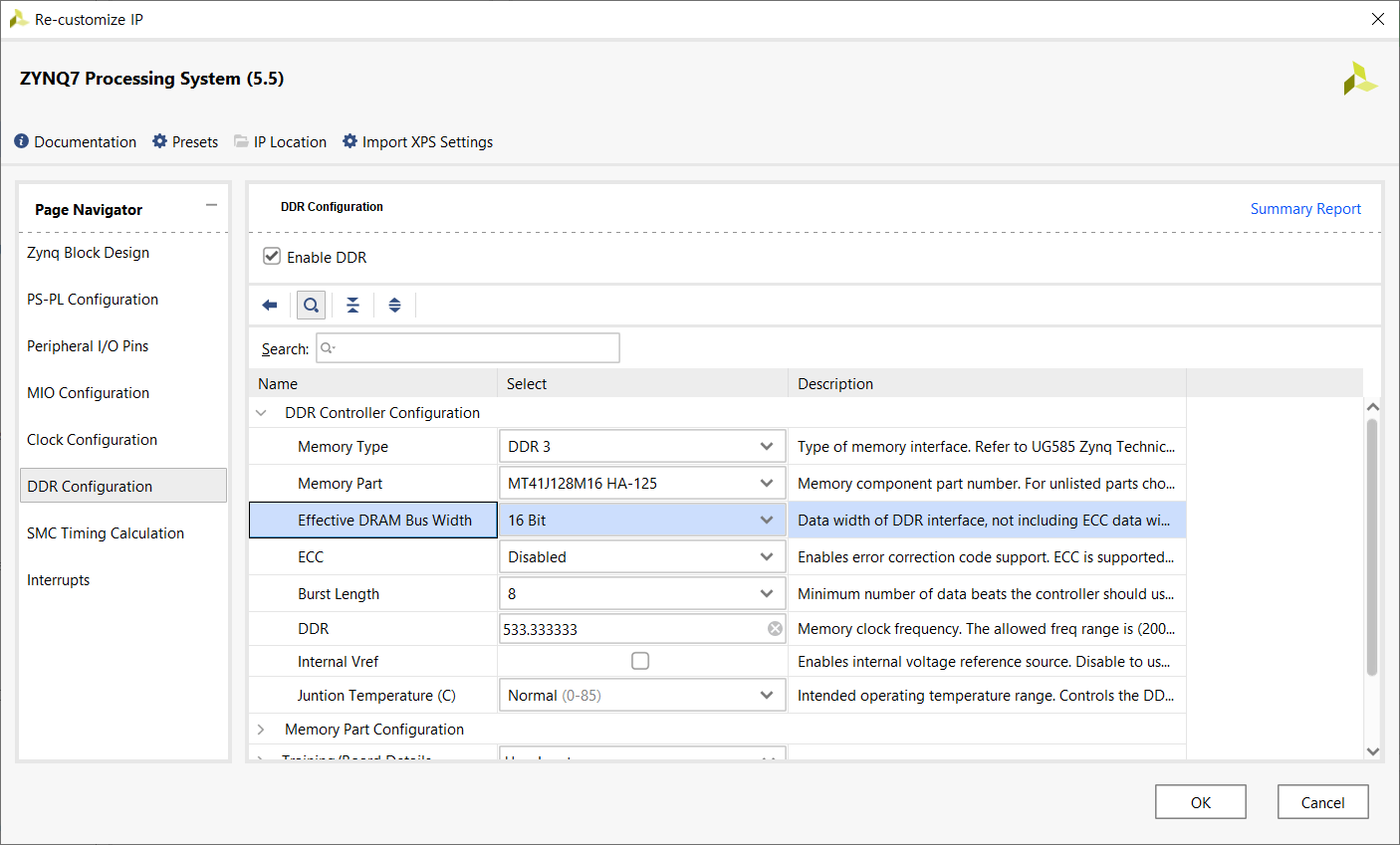

이후 DDR Configuration > DDR Controller Configuration > Memory Part 를 MT41J128M16 HA-125로 바꿔준다.

아래의 Effective DRAM Bus Width 도 16Bit 로 바꿔준다.

긴 설정 작업을 다 했다. OK 를 눌러 나간다.

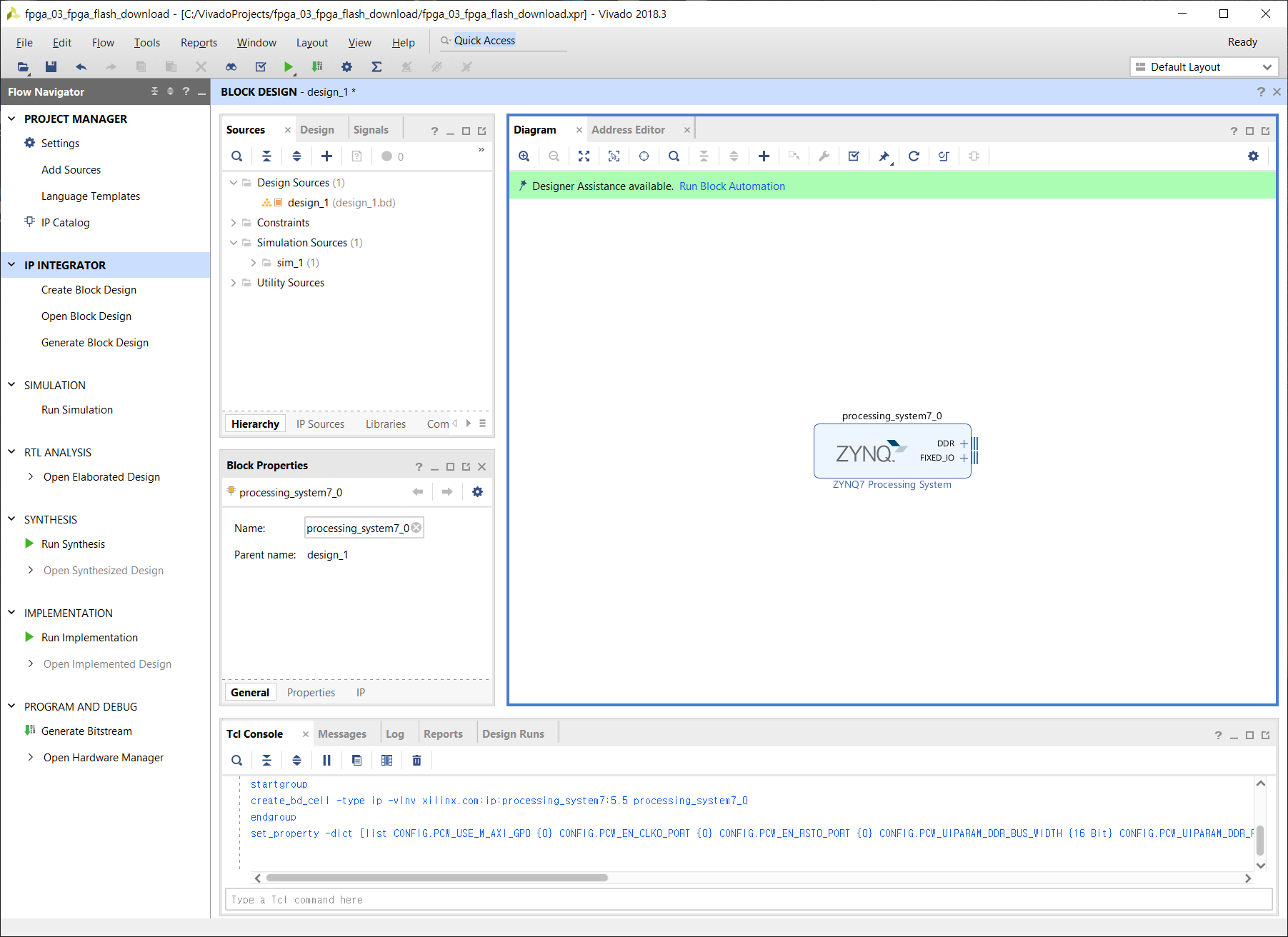

위의 초록색 바에 Designer Assistance avilable. Run Block Automation 이라고 나와 있는데, Run Block Automation 을 누른다.

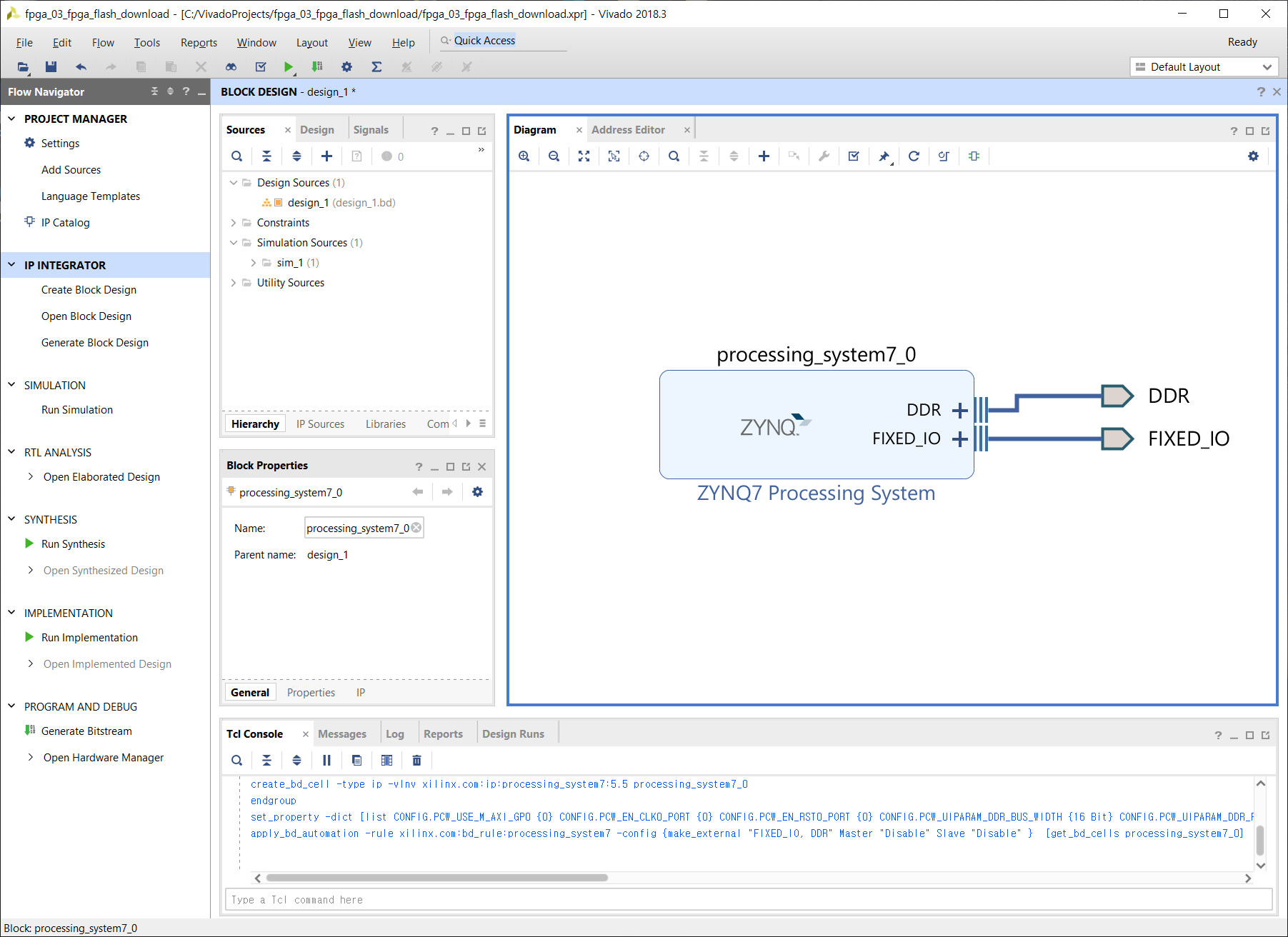

선택을 하고 OK를 누른다.

그러면 ZYNQ PS OUTPUT 으로 DDR, FIXED_IO 가 생긴다.

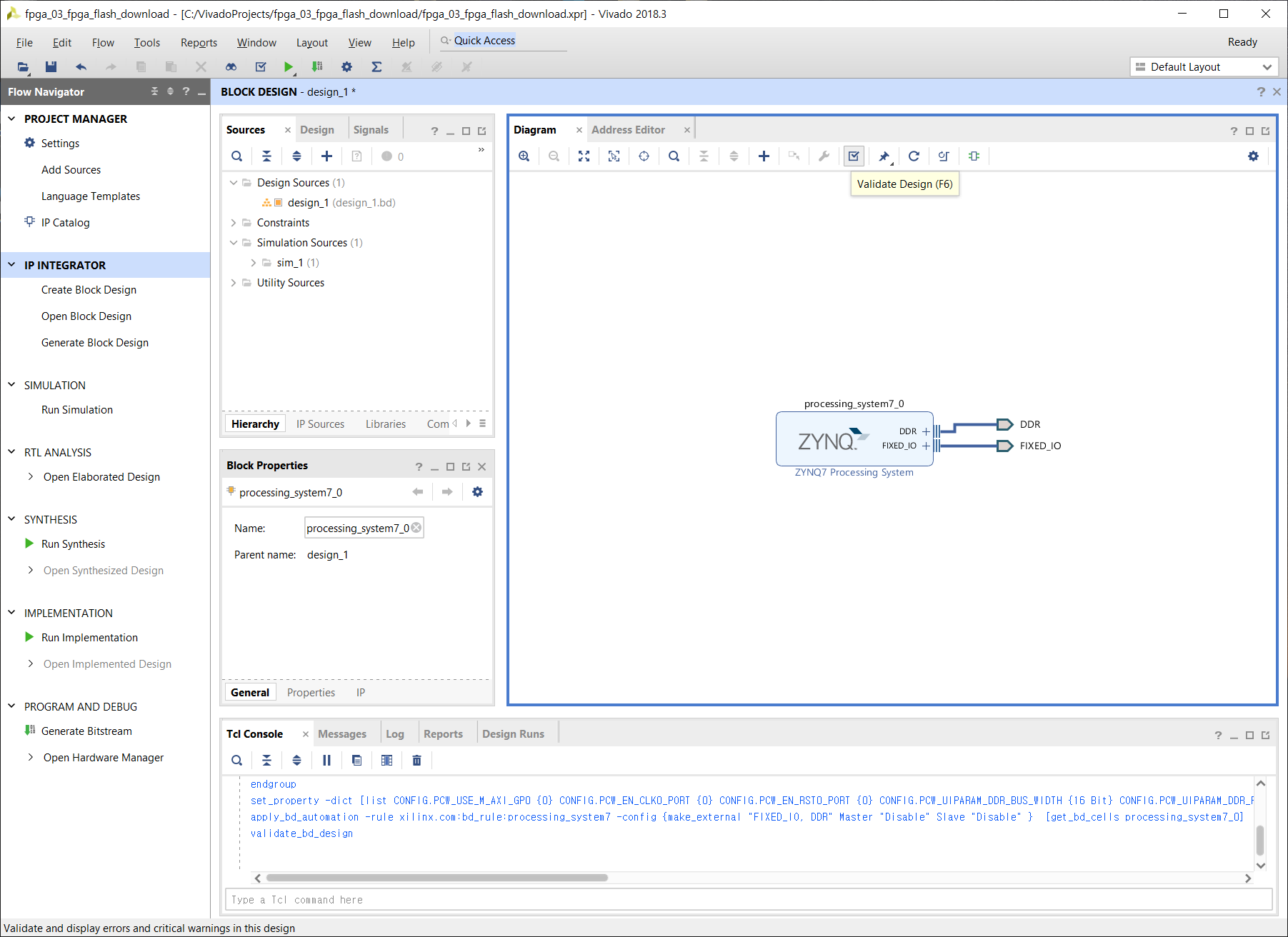

이후 디자인 검증을 한 번 해준다.

성공했다면 OK 를 누른다.

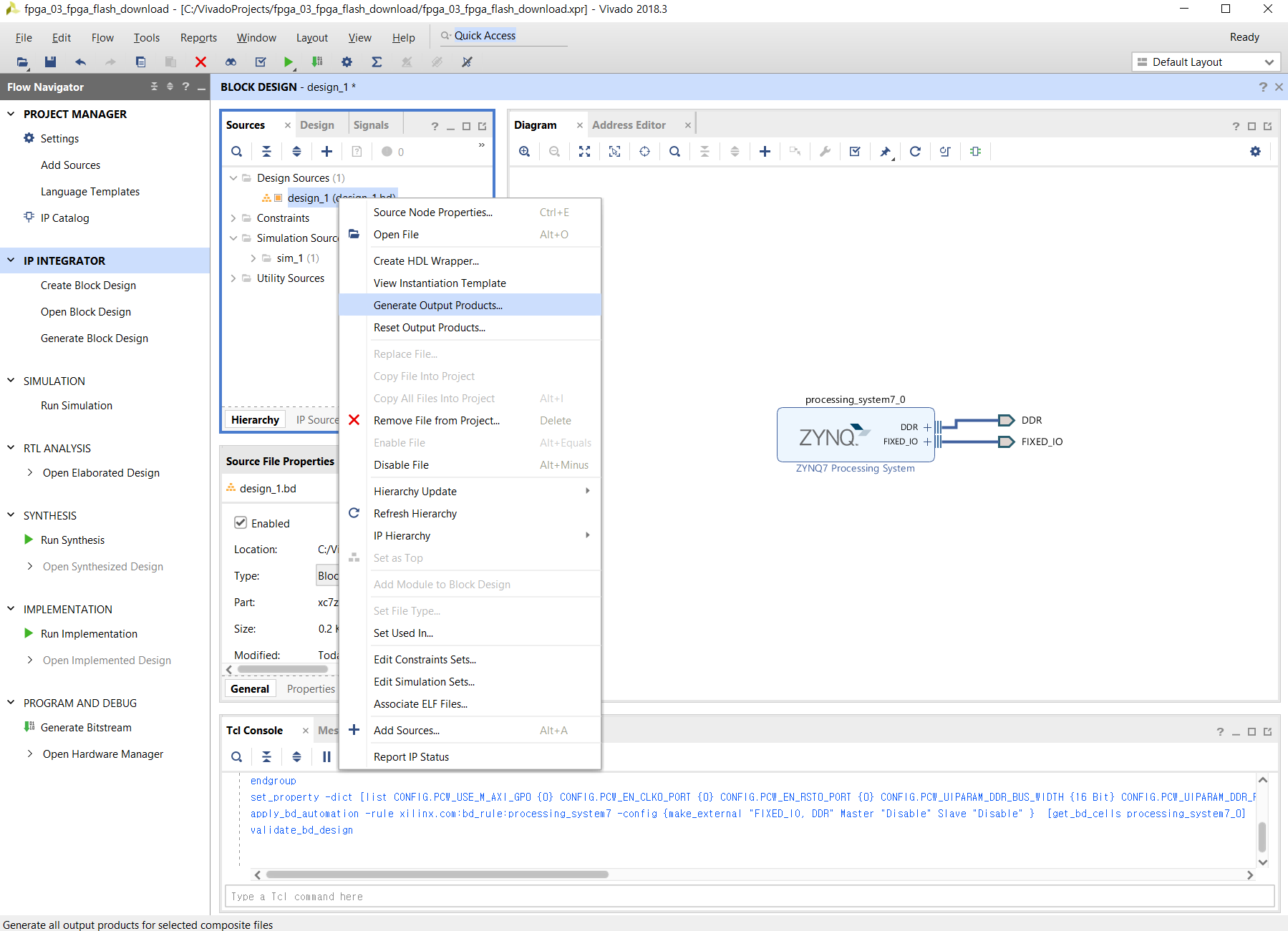

이후 소스에서 내가 만든 .bd 파일에서 Generate Output Products 를 선택한다.

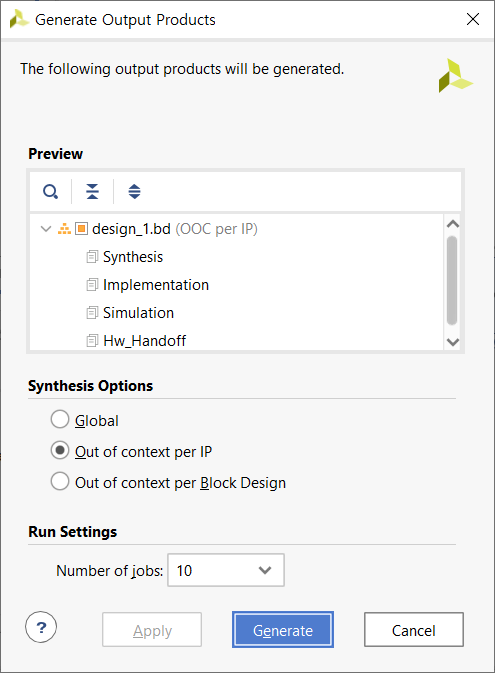

바로 Generate 버튼을 눌러 준다.

Number of jobs 는 자신의 스레드 개수에 따라 바뀌니 상관을 크게 하지 않아도 된다.

끝나면 끝났다고 알려준다.

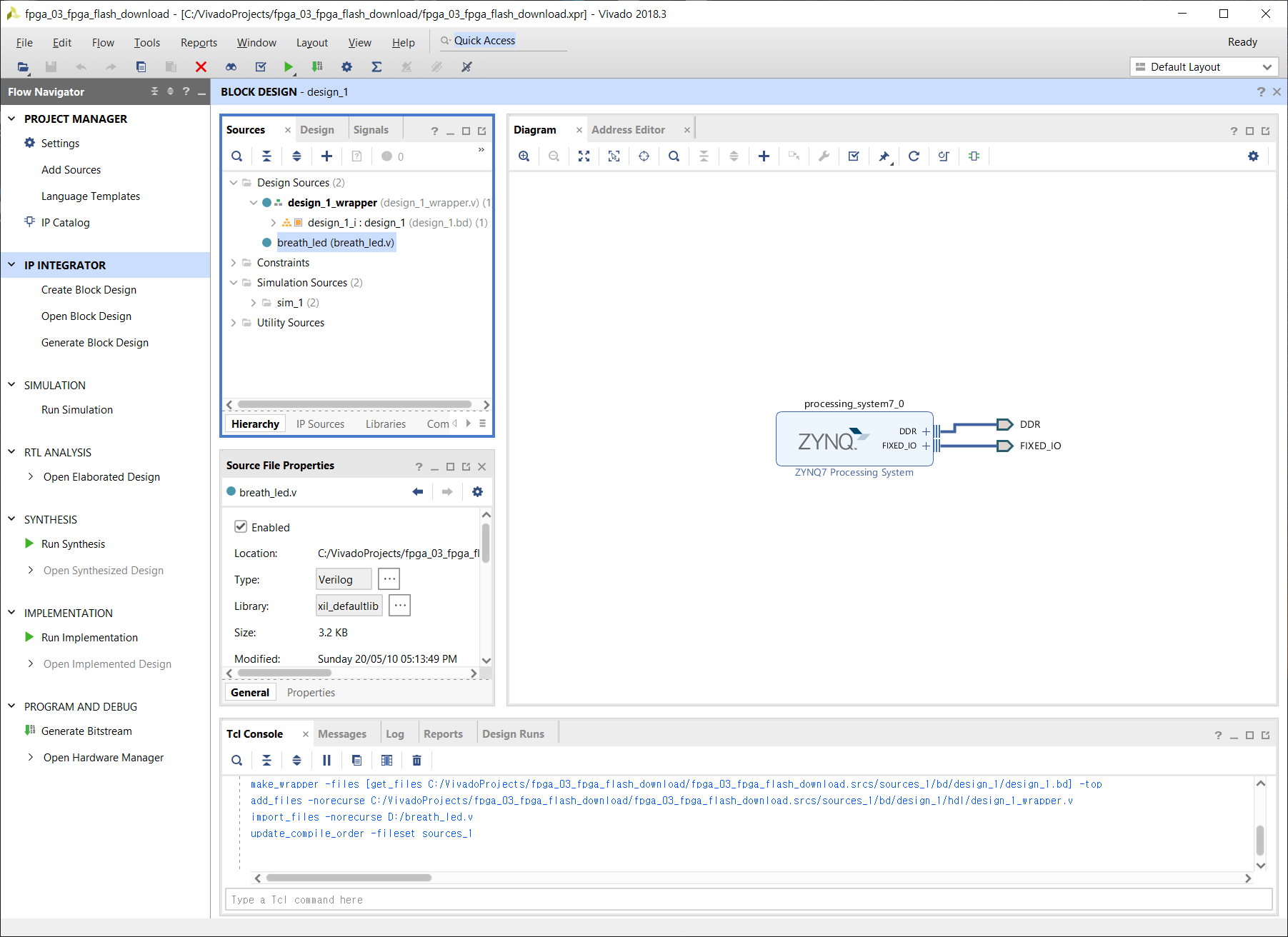

다음으로 Create HDL Wrapper 를 실행한다.

OK 선택.

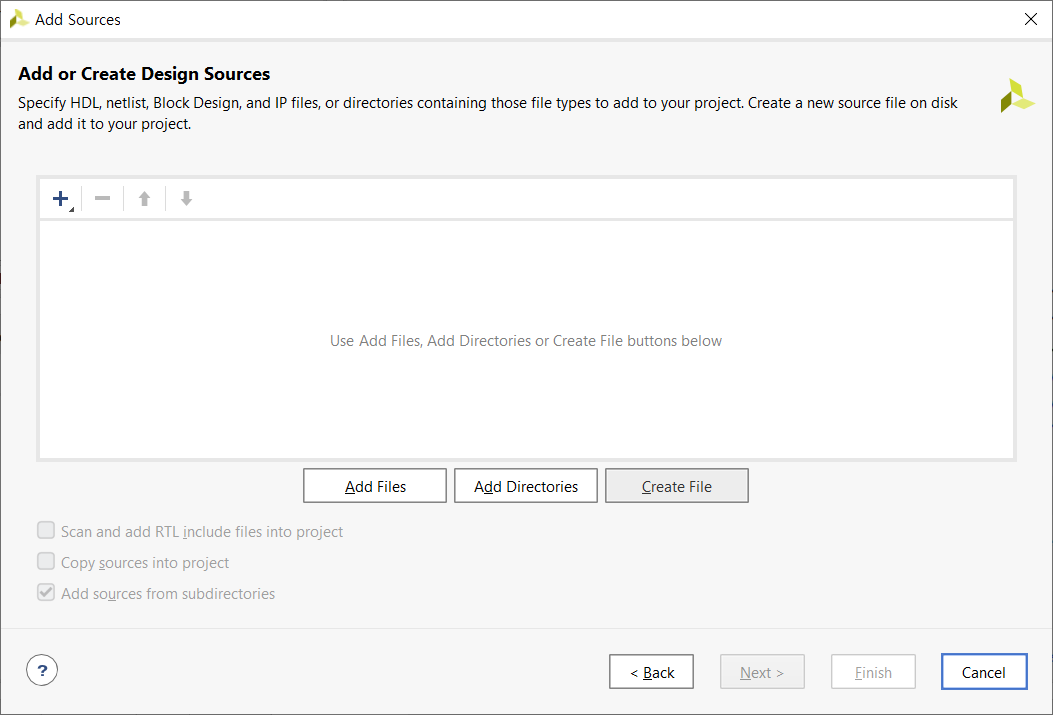

그리고 소스를 하나 더 추가한다.

디자인 소스를 추가하는데, 파일은 이것이다.

파일을 추가하고 Copy sources into project 옵션도 on 으로 설정한뒤 Finish 선택.

이렇게 소스에 breath_led 가 추가로 생겼다.

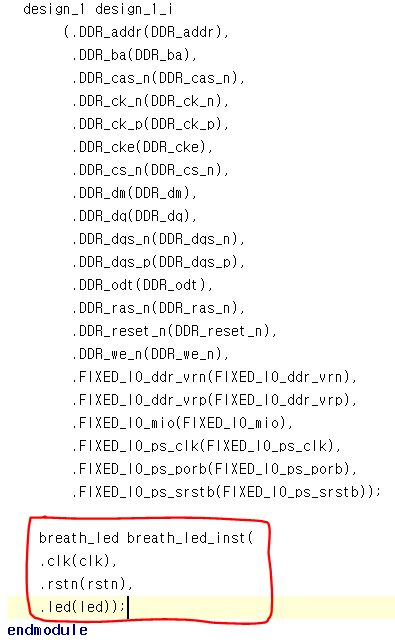

그리고 design_1_wrapper.v 를 살짝 수정해 준다.

...

FIXED_IO_ps_porb,

FIXED_IO_ps_srstb,

clk,

rstn,

led

);

input wire clk;

input wire rstn;

output wire [3:0] led;

inout [14:0]DDR_addr;

...

breath_led breath_led_inst(

.clk(clk),

.rstn(rstn),

.led(led));

를 각각 추가하고 저장해준다.

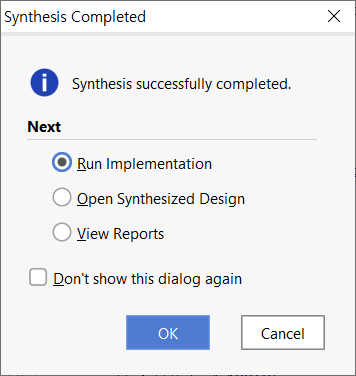

이후 합성을 진행한다(Synthesis > Run Synthesis)

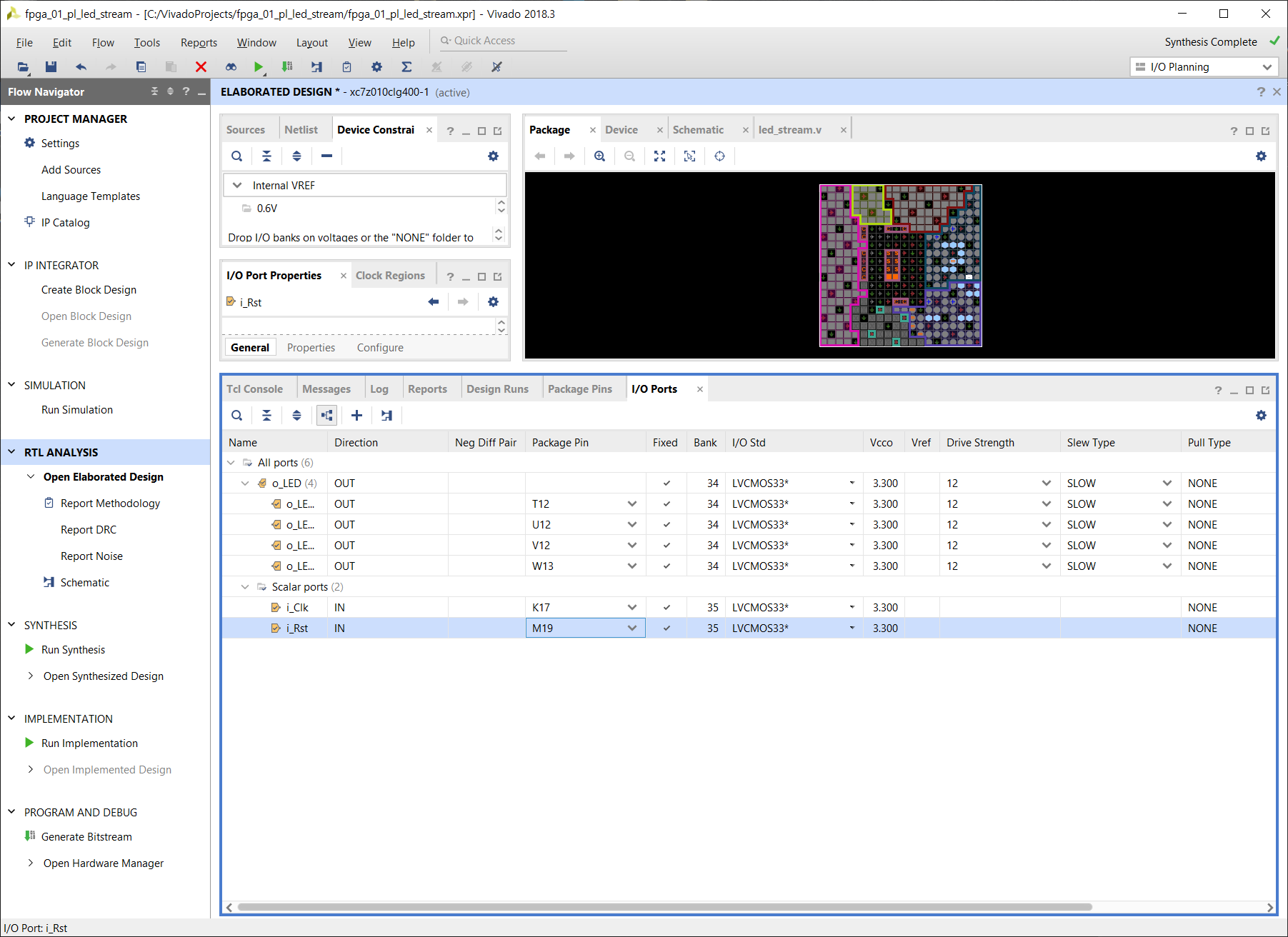

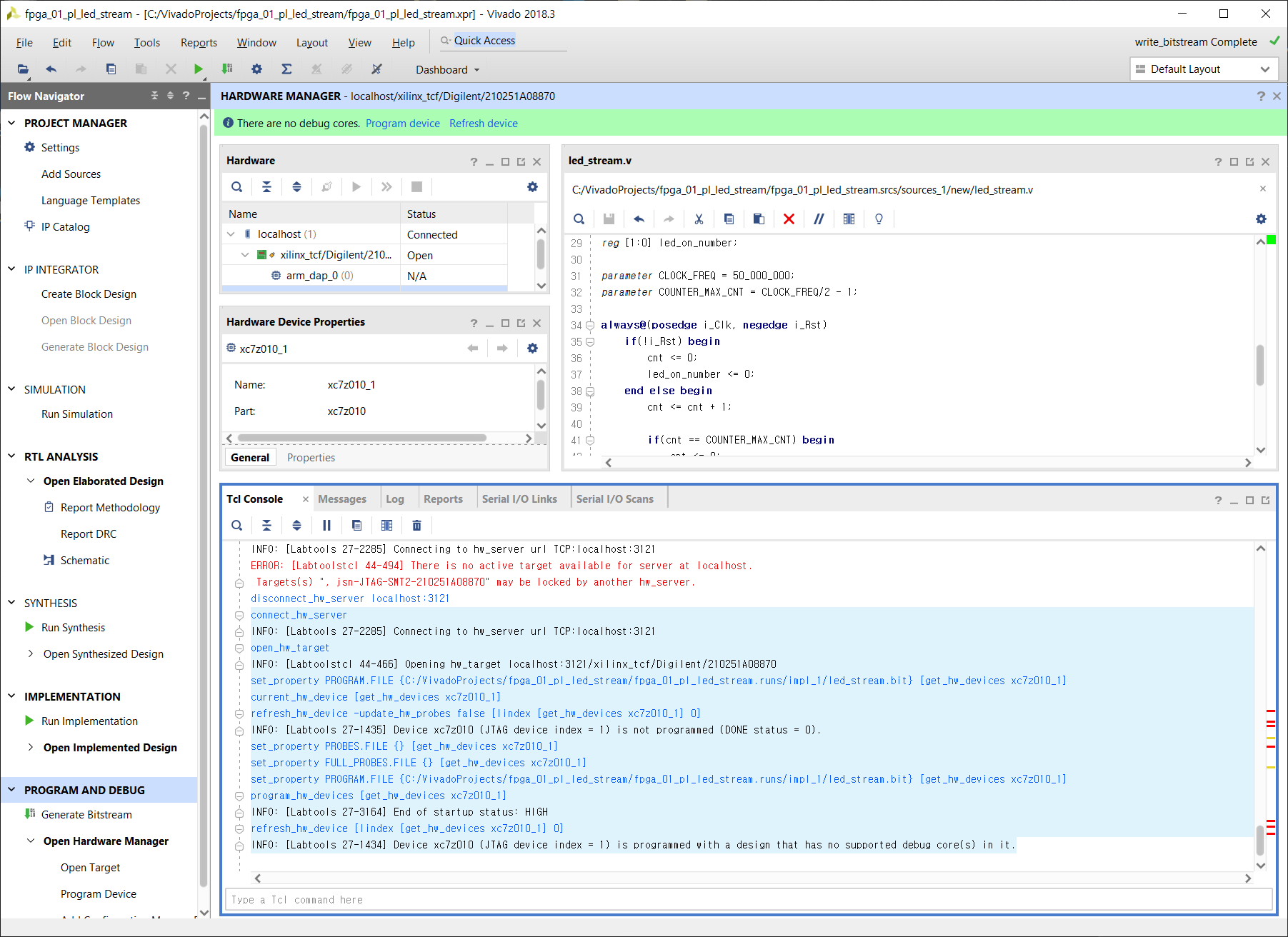

이후 I/O 핀 매핑을 위해 RTL ANALYSIS의 Open Elaborated Design > 우측 상단 I/O Planning 에 들어가 I/O Ports 변경

I/O port 는 led [0]~[3], clk, rstn 만 수정한다.

그림과 같다.

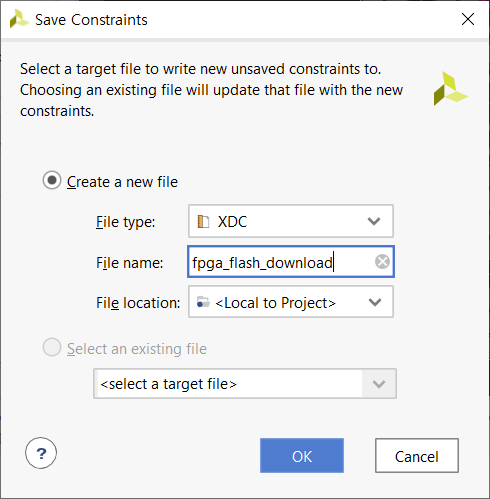

다 기입했다면 저장하고 File name을 fpga_flash_download 로 설정해 준다.

OK 를 누른다.

이후 Bitstream 까지 다시 만들어 준다.

(Synthesis > Implementation > Bitstream)

이번에는 Bitstream 을 바로 보드에 올릴 것이 아니기 때문에 Bitstream 생성이 끝난 뒤에 cancel 을 눌러 창을 닫는다.

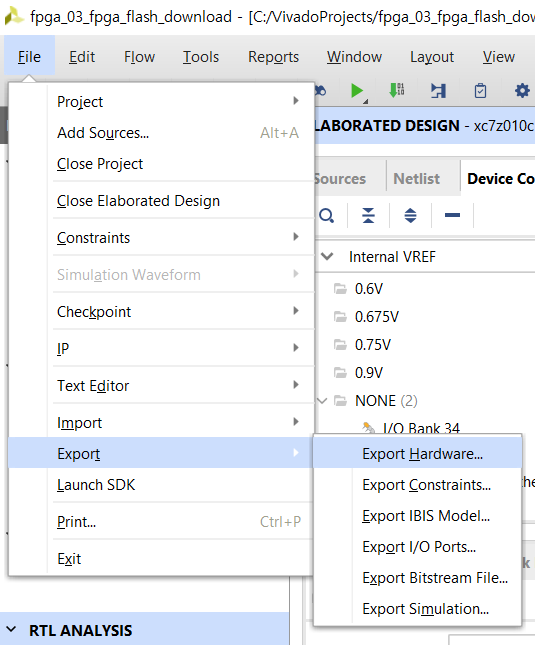

HW Export 를 선택한다.

bitstream 포함을 하고 OK 를 누른다.

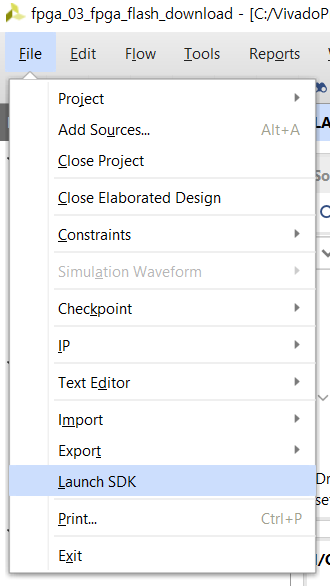

이후 SDK 를 켠다.

Launch SDK 창이 뜨면 OK를 눌러 SDK를 킨다.

그러면 Eclipse 기반의 SDK 창이 켜진다.

SDK는 이렇게 생겼고, HW description file인 system.hdf 가 생성되어 있는 것을 확인 가능하다.

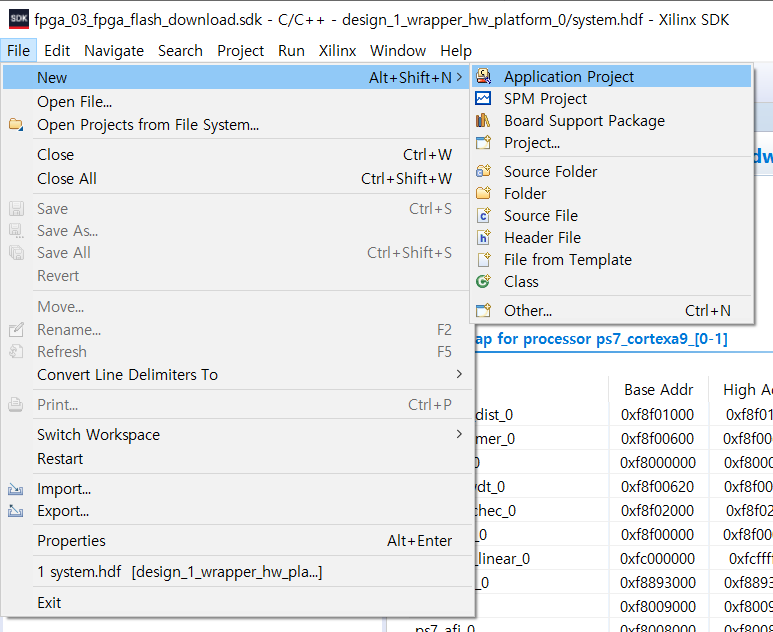

이제 SDK 상에서 새로운 프로젝트를 만들어 본다.

File > New > Application Project

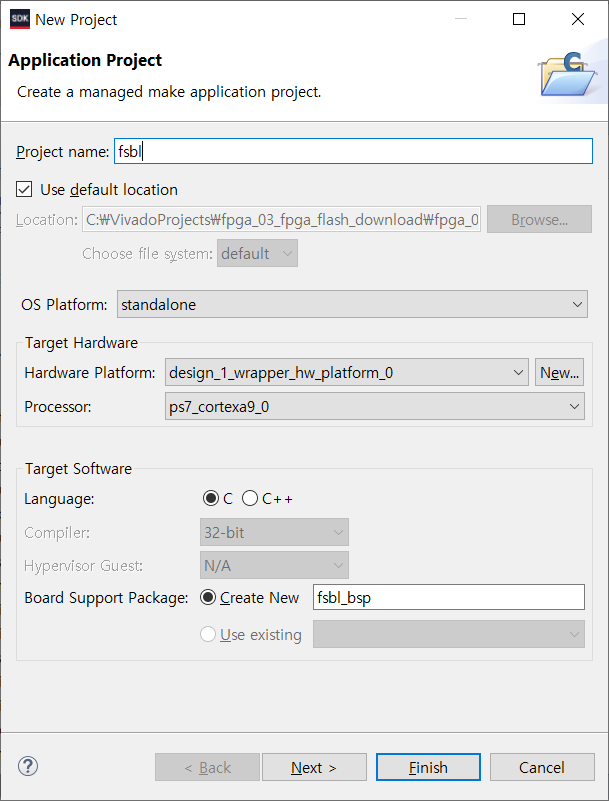

프로젝트 이름은 fsbl 로 한다.

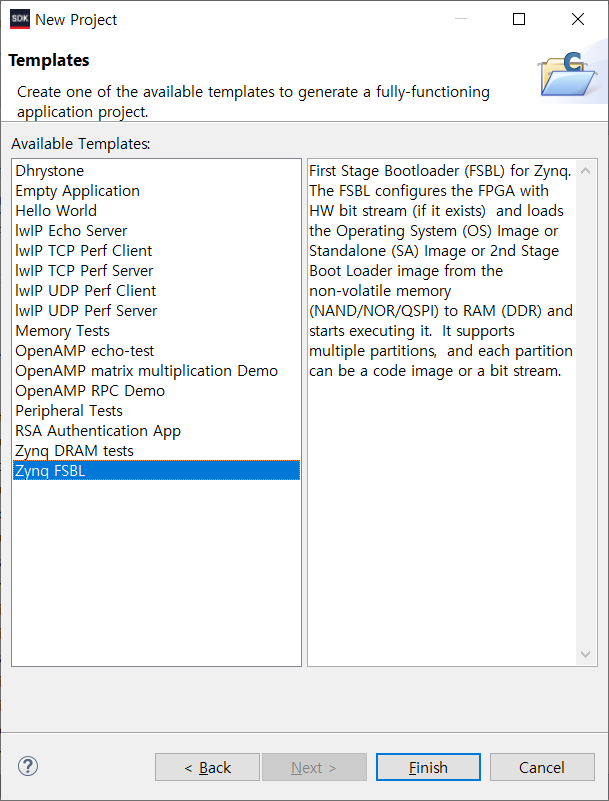

Next 를 누르고 Zynq FSBL 을 선택한다.

Finish 를 누른다.

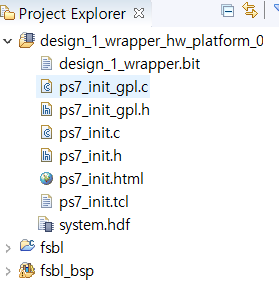

왼쪽 프로젝트에 fsbl, fsbl_bsp 가 생성된 것을 볼 수 있다.

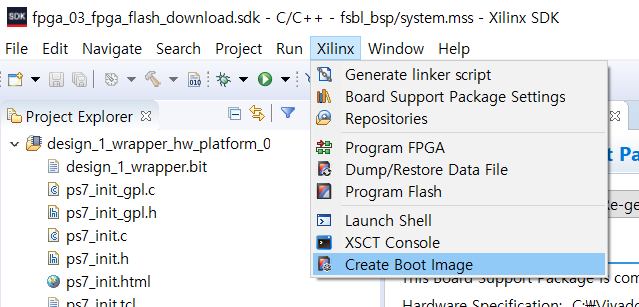

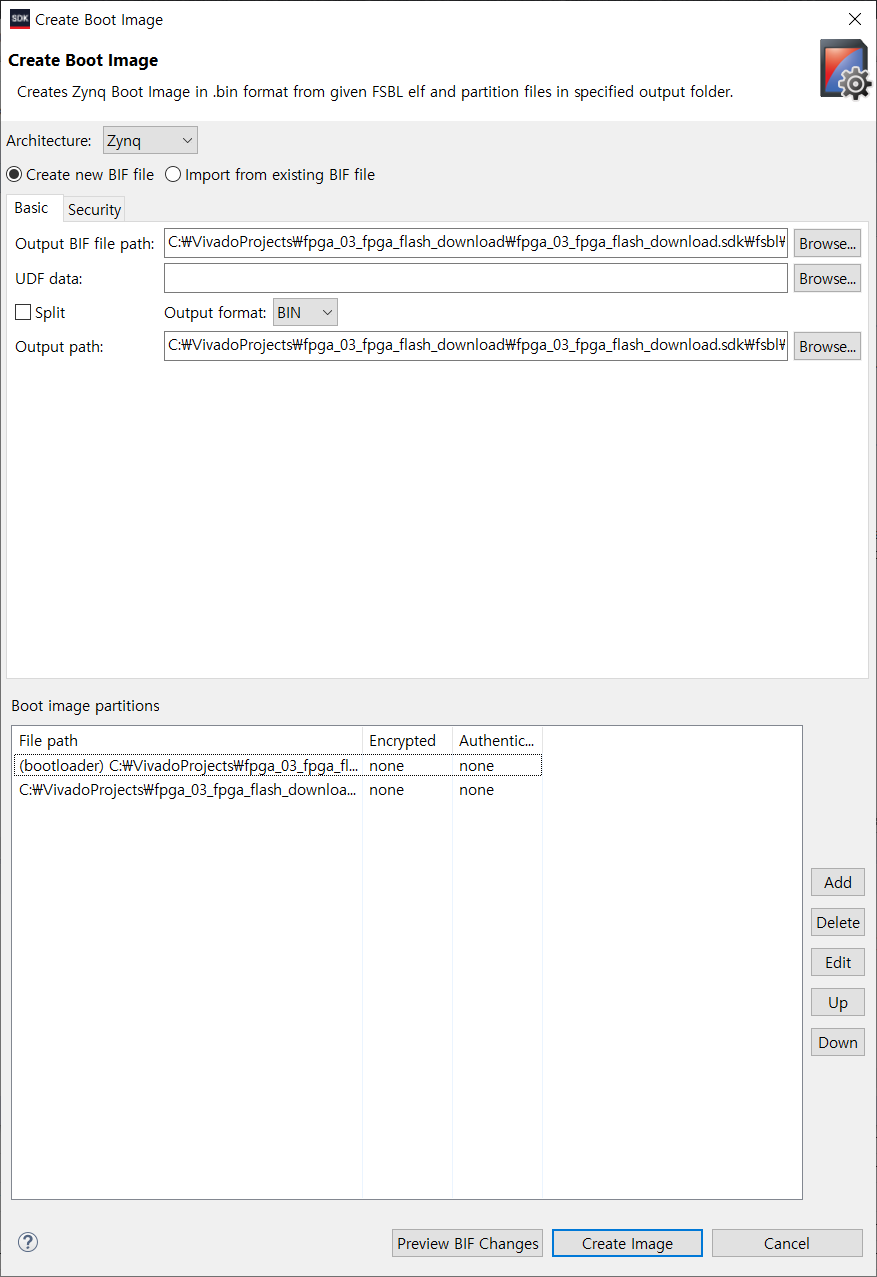

다음으로, Xilinx > Create Boot Image 를 선택한다.

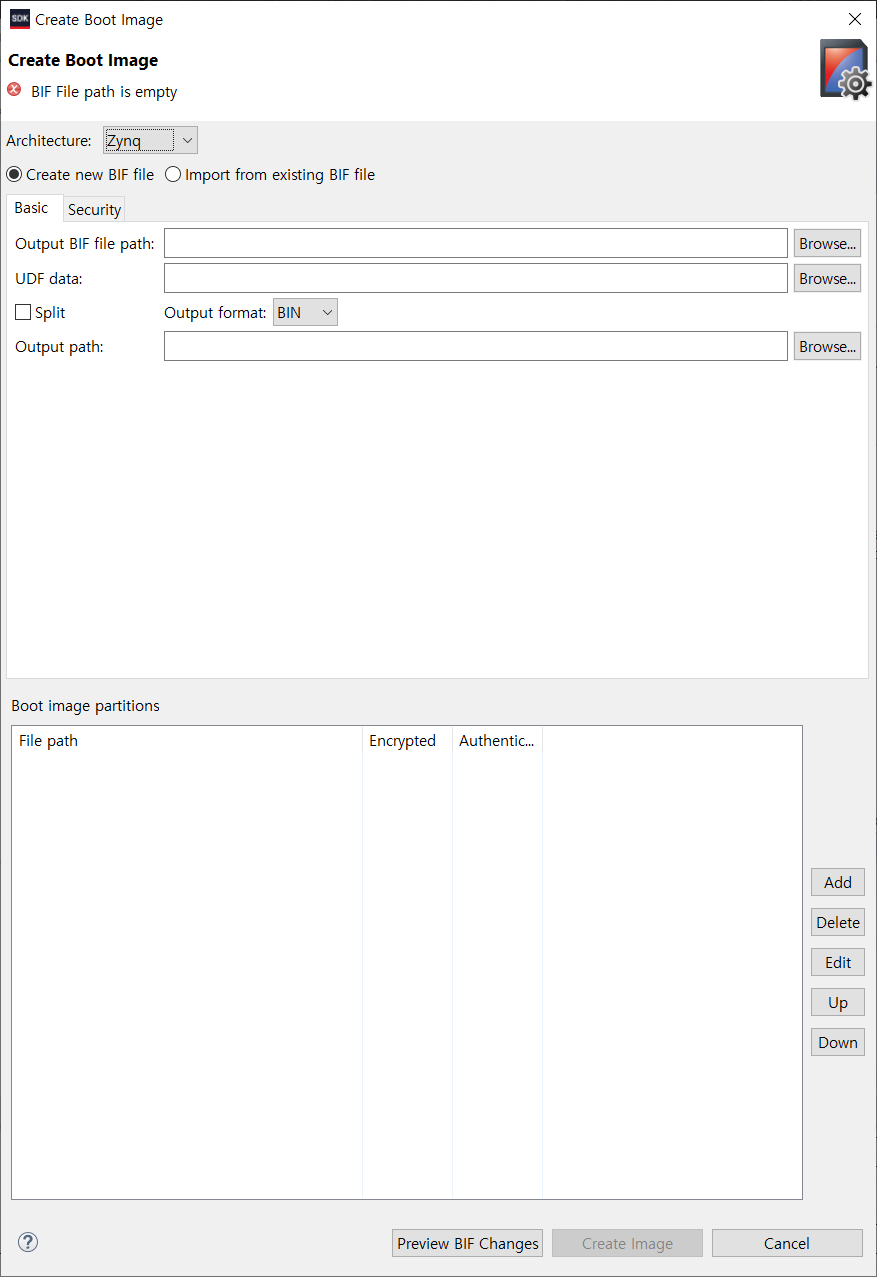

이런 이상한 창이 나오는데, Output BIF file path 를 찾아보자.

.\fpga_03_fpga_flash_download\fpga_03_fpga_flash_download.sdk\fsbl\Debug

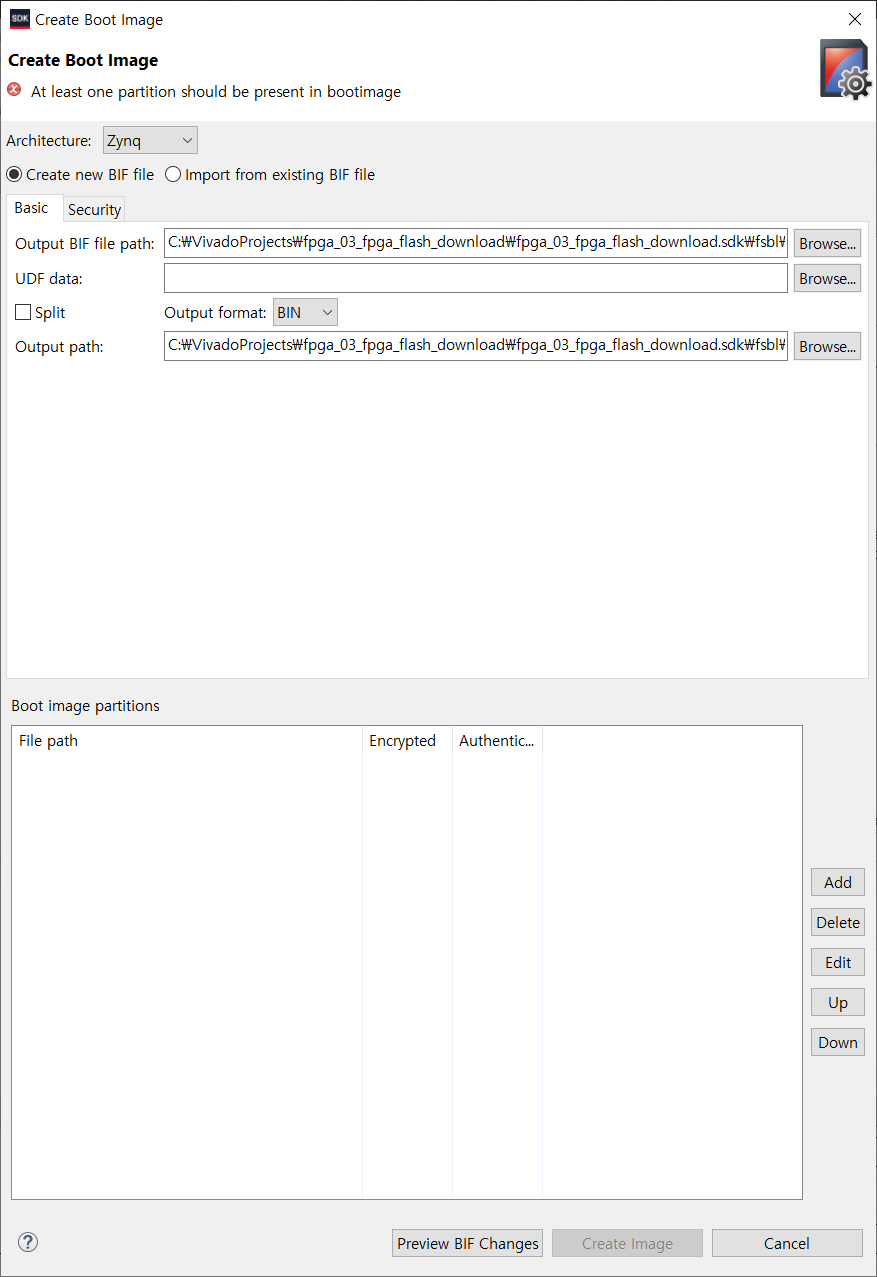

경로 지정을 해 준다.

경로 지정을 했다면 아래 Boot image partitions 의 우측 Add 를 선택한다.

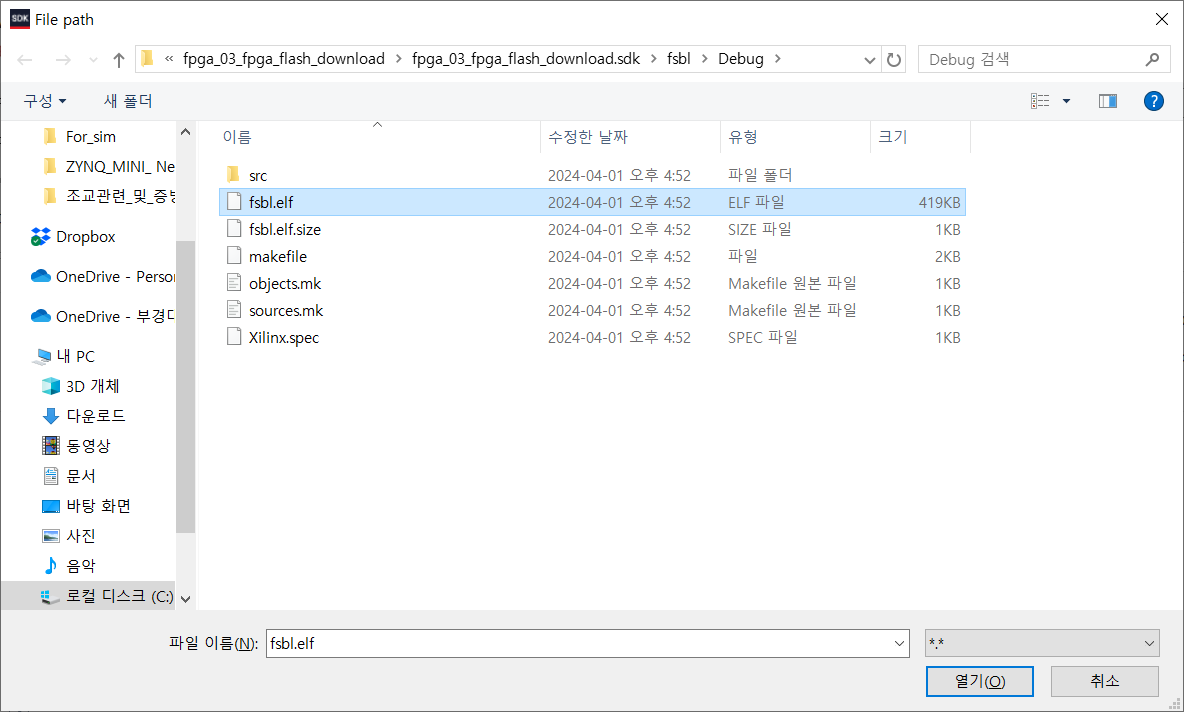

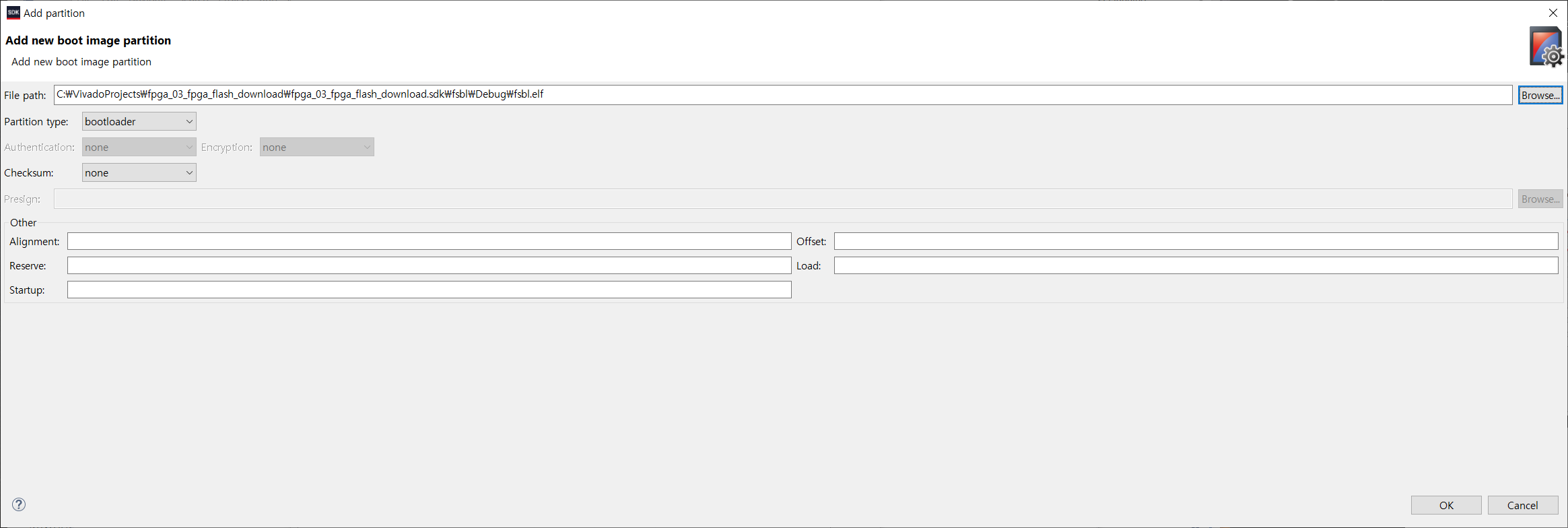

들어가서 File path > Browse..

보통 이쪽 경로는 자동으로 잡힌다.

아까 있었던 경로에서 .elf 파일을 찾고 열기를 눌러준다.

File Path 가 이렇게 잡히고, Partition type 는 bootloader 로 설정해 준다. 그리고 OK를 눌러 나가자.

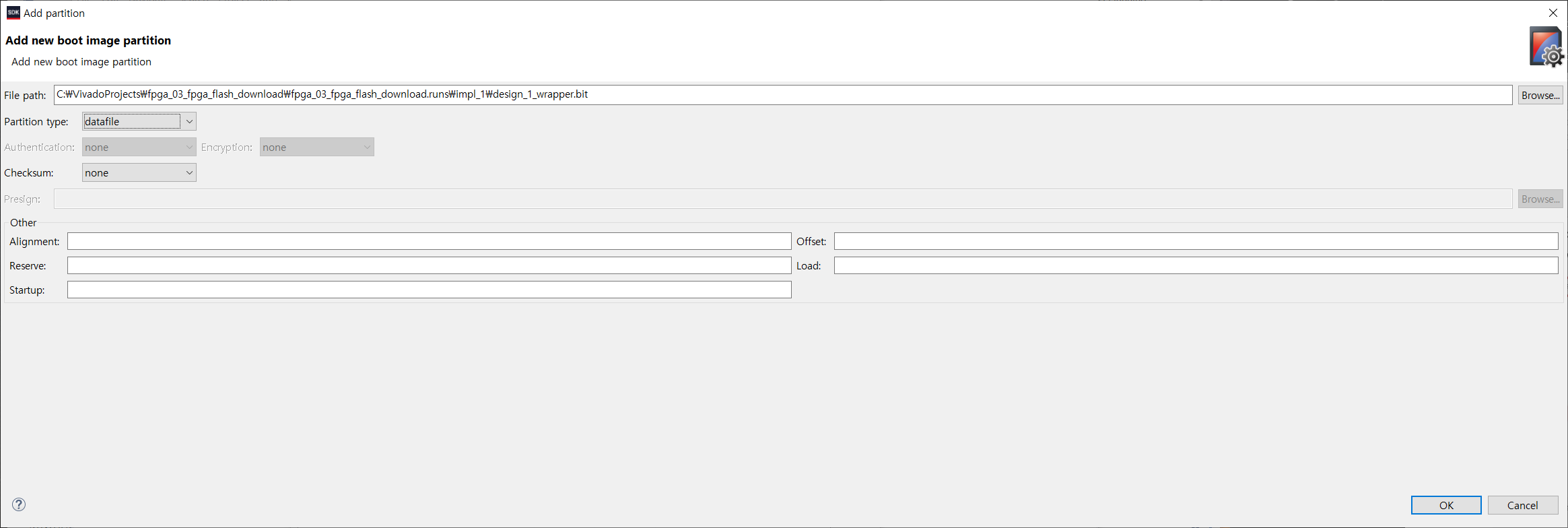

파일을 하나 더 추가할 것이다. 다시 Add 를 눌러 아까 만들었던 wrapper 의 bitstream을 추가 할 것이다.

이 파일은 .\fpga_03_fpga_flash_download\fpga_03_fpga_)flash_download.runs\impl_1 에 위치해 있다.

찾아서 열고, Partition type 을 datafile 로 지정해 주자.

다 되었다면 OK를 눌러준다.

이렇게 추가되었다면 완료다.

Create Image 를 눌러 바이너리 파일을 생성하자.

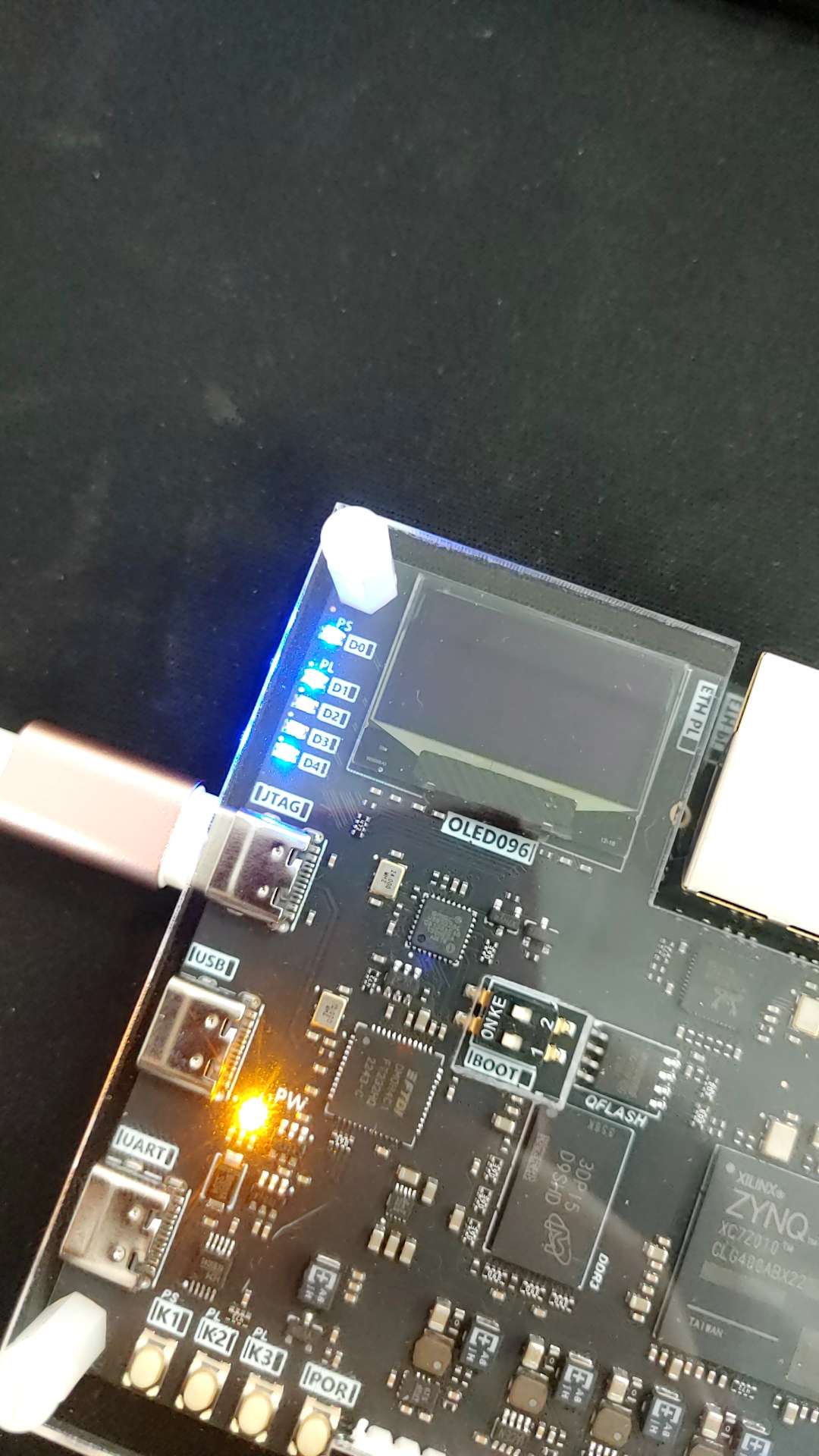

이후 보드에 파일을 올리기 위해 처음은 JTAG(00) 모드로 킨다.

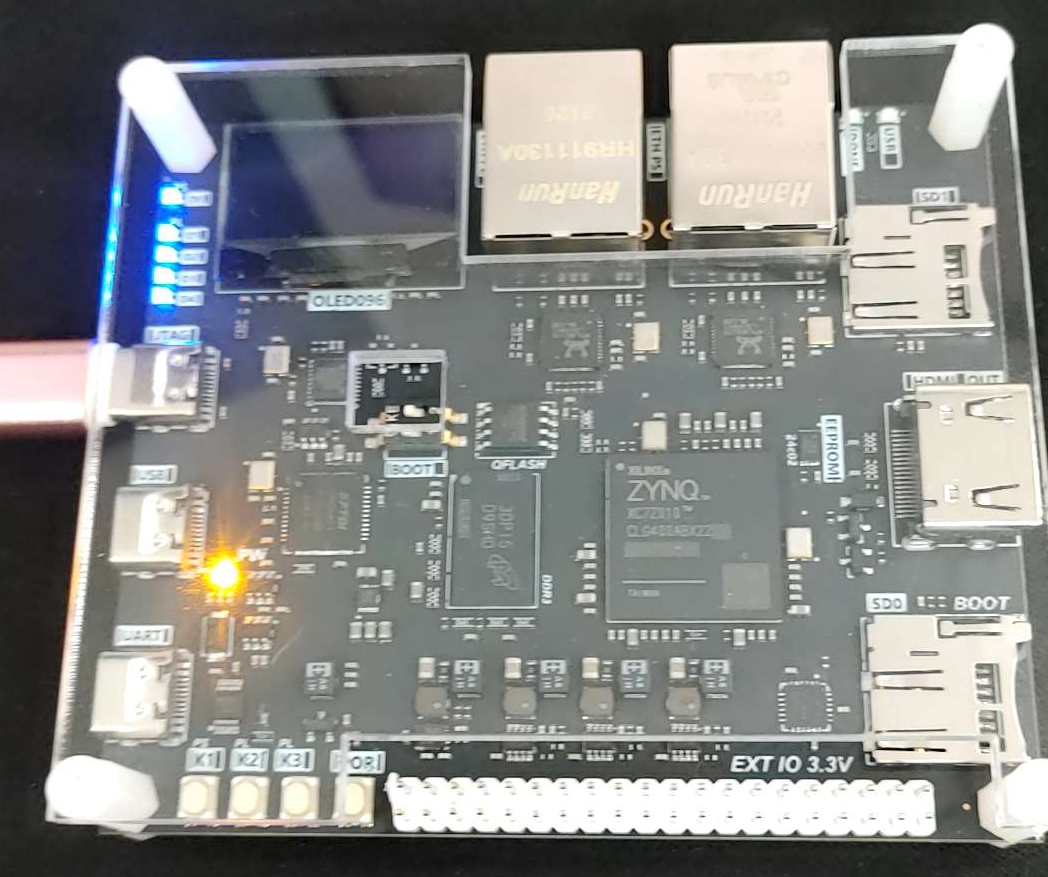

JTAG 에 USB를 꼽고 JTAG 모드로 전원을 켠다.

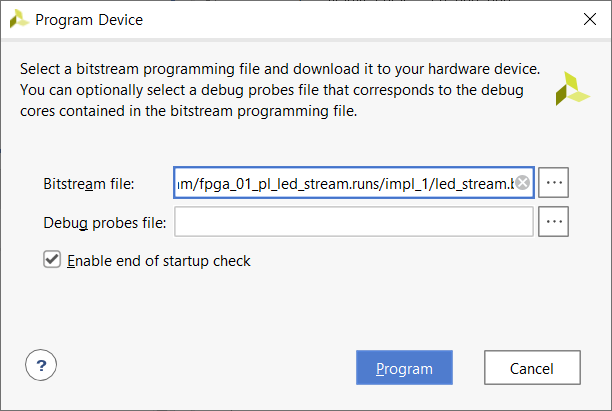

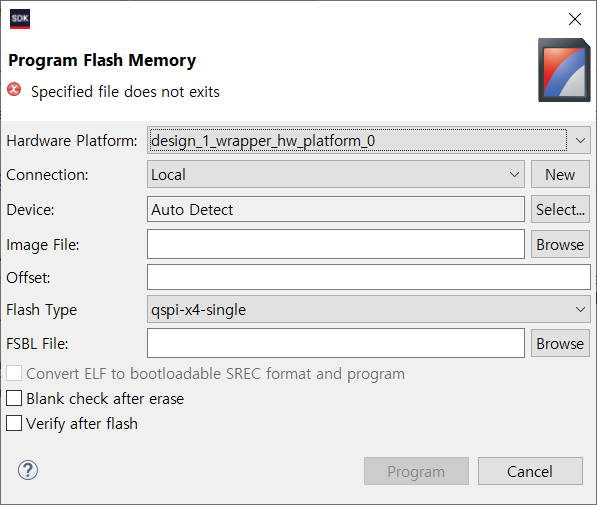

그림과 같이 Program Flash 를 켜준다.

그럼 그림과 같은 창이 나오는데, Image file 은 아까 우리가 생성했던 Binary 파일을 넣어준다.

경로는 다음과 같다. .\fpga_03_fpga_flash_download\fpga_03_fpga_flash_download.sdk\fsbl\Debug

BOOT.bin 파일을 열어주고

FSBL file 도 지정을 해 줘야 한다. 이 친구도 BOOT.bin 과 있는 위치가 동일하기 때문에 바로 열 수 있다.

.elf 파일을 넣어 주도록 하자.

다 끝나면 이렇게 되어 있다.

Program 을 눌러 실행 시킨다.

Progress Information 이라는 창이 나오는데, 첫 실행에 굉장히 느리다.

나의 경우 30분 정도 기다렸는데 진행 될 생각을 안 해서 껐다가 키니까 빨리 진행 되었다.

Programming Flash를 진행 할 때에는 JTAG 모드로 키는 것을 잊지 말자.

이후 완료되었다면 보드의 BOOT 를 QSPI(10) 으로 설정하고 POR(reset button) 을 한 번 눌러 보자.

LED breathing 이 구현 되었을 것이다.

또한 보드의 ROM에 Write 한 것이기 때문에 전원이 끊겼다가 다시 QSPI 모드로 키더라도 내장된 코드가 바로 구현된다.

'ZYNQ_MINI' 카테고리의 다른 글

| [ZYNQ MINI] 보드로 petalinux 돌려보기 - [2] (0) | 2024.04.01 |

|---|---|

| [ZYNQ MINI] 보드로 petalinux 돌려보기 - [1] (0) | 2024.04.01 |

| [ZYNQ MINI] Vivado로 첫 프로젝트 생성 (0) | 2024.04.01 |

| [ZYNQ MINI] 설명서 읽어보기 (0) | 2024.04.01 |

| [ZYNQ MINI] 보드 도착 및 툴 설치 (0) | 2024.04.01 |