OV7670 카메라 지원을 위해 SCCB Interface 에 대해 먼저 보려고 함.

다음 레퍼런스를 참고하였다.

https://www.waveshare.com/w/upload/1/14/OmniVision_Technologies_Seril_Camera_Control_Bus%28SCCB%29_Specification.pdf

DeepL 번역본을 사용해도 좋다.

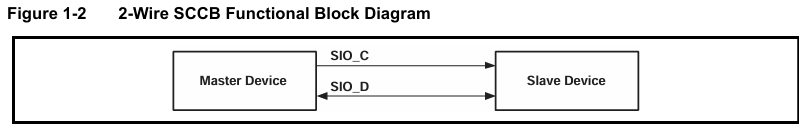

OV7670은 2-Wire SCCB Interface 를 사용한다.

2-Wire SCCB Interface 는 단 하나의 Slave Device 와 통신하므로 다음과 같은 블록도를 가진다.

2-wire 구현을 위해서 다음 두 가지 방법 중 하나는 되어야 한다.

1. master 가 tri-state 모드에서 버스의 데이터 라인을 지원하고 유지할 수 있어야 함

2. 마스터가 데이터 라인의 tri-state 상태를 유지할 수 없는 경우 데이터 라인을 하이 또는 로우로 구동하고, 슬레이브 카메라 칩과의 통신을 하기 위해 전환되는 것을 기록하는 것

마스터

| Signal name | Signal type | Description |

| SIO_C | Output | 버스가 IDLE 상태일 때 마스터가 logical 1 로 SIO_C를 구동시킴. 시스템이 일시 중단 모드일 때 logical 0으로 구동 |

| SIO_D | inout | 버스가 IDLE일 때 움직이지 않고, 일시 중단 모드일 때 logical 0로 구동 |

| PWDN | Output | Power down |

슬레이브

| Signal name | Signal type | Description |

| SIO_C | Input | 시스템이 일시 중단 모드일 때 입력 패드 종료 가능 |

| SIO_D | inout | 시스템이 일시 중단 모드일 때 입력 패드 종료 가능 |

| PWDN | Input | 입력 전원 차단 |

SIO_C

마스터에서 구동해야 하는 단방향, Active HIGH, 컨트롤 신호 임

버스가 IDLE 상태일 때 logical 1 로 SIO_C를 구동시킴

전송 시작 후 SIO_C가 logical 0으로 구동되면 데이터 전송 시작

데이터 전송 중 SIO_C의 논리 1은 전송된 단일 비트를 나타냄

따라서 SIO_C가 0으로 구동될 때만 SIO_D가 발생 가능

단일 전송 비트의 주기를 t_CYC 라고 하고

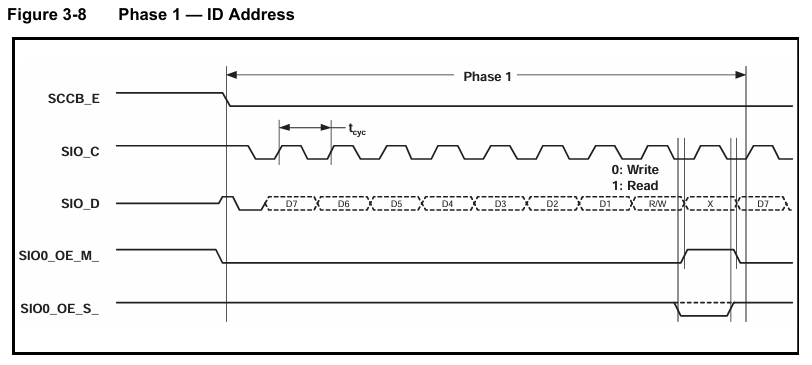

t_CYC의 최소값은 10us을 가짐[Fig. 3-8]

SIO_D

SIO_D는 마스터 / 슬레이브에서 구동할 수 있는 양방향 신호

Don't care bit 상태(나중에 다룸)를 가질 수 있음

Transmission Cycles(전송 주기)

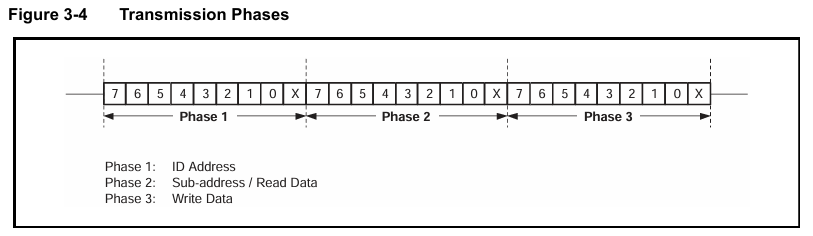

하나의 Phase : 9-bit 로 구성

9번째 비트(X 표시)는 데이터 전송이 R/W 인지에 따라 Don't care bit 또는 N/A bit 임.

전송에는 최대 3개의 Phase 가 포함될 수 있음

MSB가 항상 먼저 전달됨

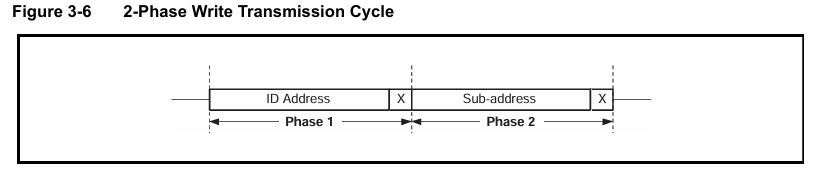

2-Wire Write Transmission Cycle

2-Phase 쓰기 전송 뒤에 2-Phase 읽기 전송이 이어짐.

쓰기를 사용하는 목적은 마스터가 데이터를 읽으려는 특정 슬레이브의 하위 주소 식별을 하기 위함

9번째 비트는 Don't care bit

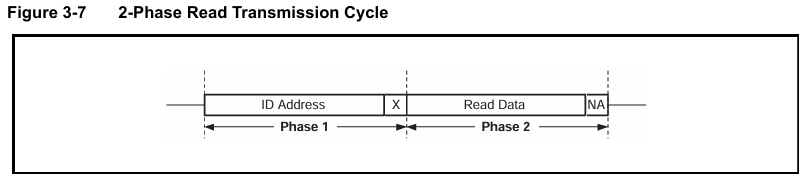

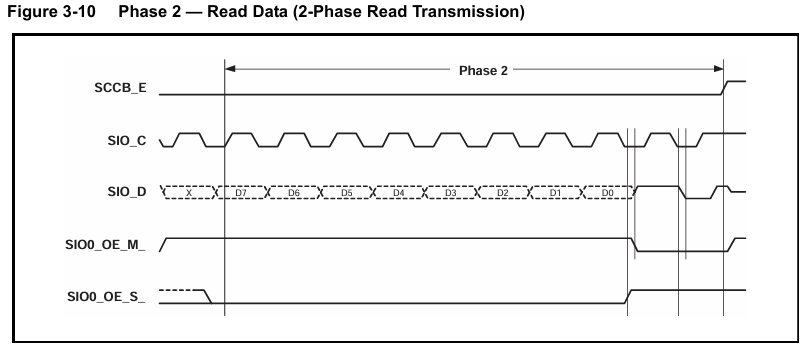

2-Wire Read Transmission Cycle

쓰기가 진행된 후 읽기가 실행됨.

쓰기와 다르게 하위 주소를 식별할 수 있는 기능 없음

8비트의 읽기 데이터와 9번째 Don't care bit 또는 N/A 비트가 포함됨

마스터는 N/A 비트를 logical 1로 구동해야 함

ID 주소

마스터가 데이터를 읽거나 쓸 선택된 슬레이브 식별하기 위한 주소

각 슬레이브는 I2C 통신처럼 2^7개의 슬레이브 존재 가능(8번째 비트는 R/W 중 선택, 0: Write, 1:Read)

Phase 1의 9번째 비트는 Don't care bit 여야 함

SIO0_OE_M_(아마 SIO_D_OE_M_을 말하는 것 같음)

마스터의 내부 Active low, I/O 활성화 신호

SIO0_OE_S_(아마 SIO_D_OE_S_ 를 말하는 것 같음)

슬레이브의 내부 Active low, I/O 활성화 신호

OE_S_ 가 OE_M_ 보다 먼저 발생하고, 마스터가 ID address 를 가져옴 (9번째 비트는 가져오지 않음)

마스터는 알 수 없는 버스 상태 전파를 방지하기 위해 Don't care bit 기간 동안 SIO_D의 입력을 마스킹하고, 입력을 강제로 0으로 설정함.

그리고 마스터는 슬레이브의 Don't care bit에 대한 응답에 관계없이 다음 단계를 계속 가져옴

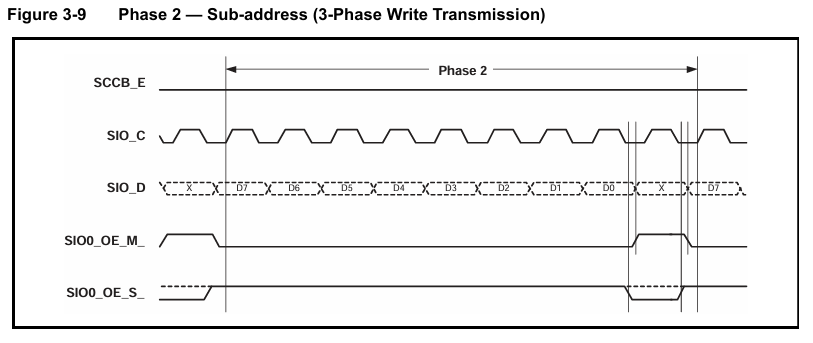

Sub-Address, Data Read

Phase 2 에서

Write : Sub-address

Read : Data

의 8비트를 받게 될 것임.

근데 2-Wire는 Slave가 하나밖에 없으므로 Sub-address 지정할 필요가 없음

따라서 Read Data 만 보도록 함

슬레이브가 Phase 2 전송을 할 때 9번째 비트는 N/A 비트로 정의

마스터는 N/A 비트 기간 동안 logical 1에서 SIO_D를 구동할 책임을 가짐

그리고 선택된 Slave가 Read data 중 SIO_D 구동을 담당함

Don't care bit

목적 : 전송이 완료되었음을 나타내는 것

쓰고 있으면서도 제대로 파악은 되지 않는다( I2C랑 비슷하다 라고는 알려져 있다.)

OV7670 을 한번 보자.

OV7670이다.

레퍼런스도 첨부한다.

OV7670.pdf (voti.nl)

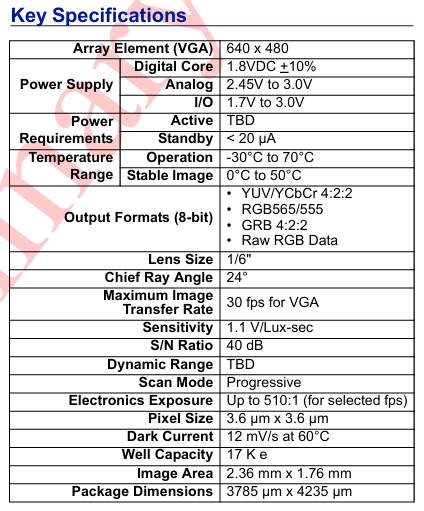

특징은 다음과 같다.

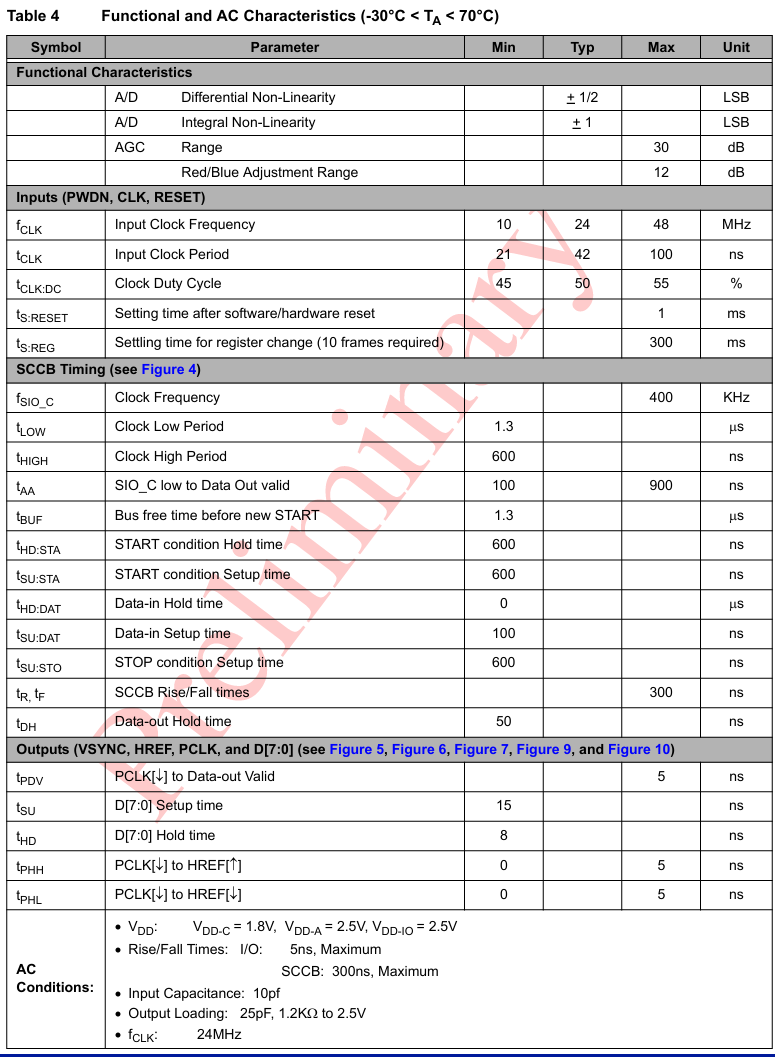

스펙은 다음과 같다.

나는 Aliexpress 에서 OV7670 모듈을 구매했고

다음 모양과 같다

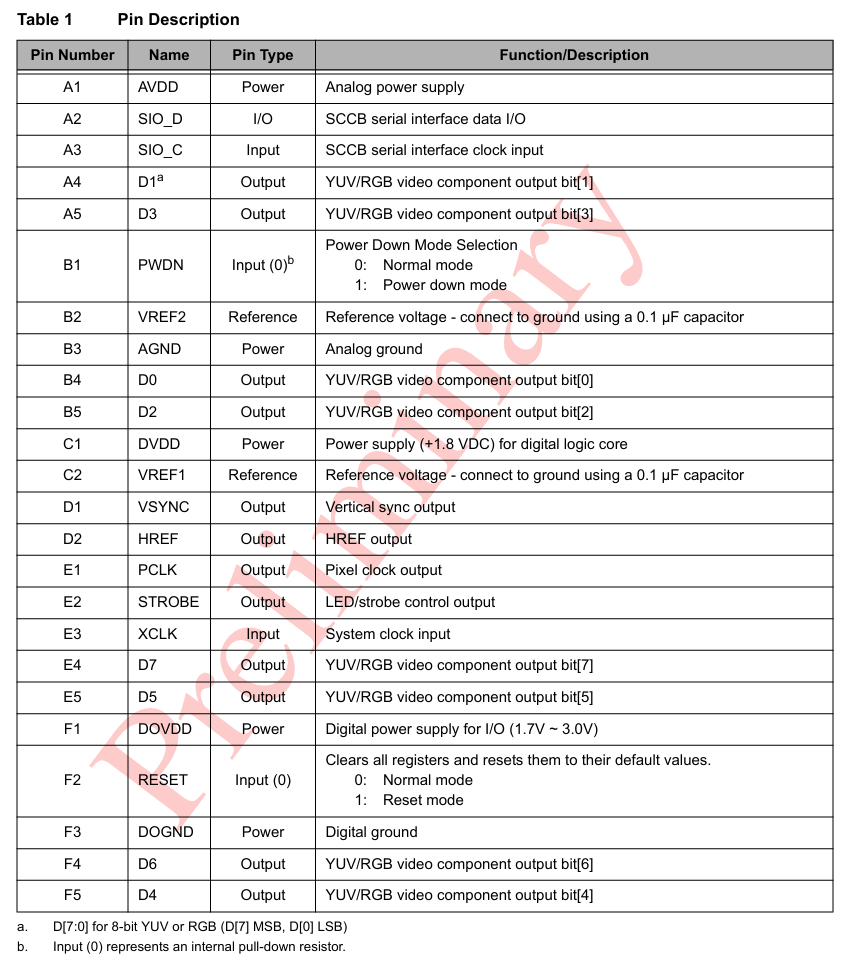

Pin 구성은 위의 사진을 보게 되면,

| 3.3V | GND |

| SCL | SDA |

| VSYNC | HREF |

| PCLK | MCLK |

| D7 | D6 |

| D5 | D4 |

| D3 | D2 |

| D1 | D0 |

| RESET | PWDN |

으로 구성된 것을 볼 수 있다.

[그림2] 에서 기능 블록도를 제공하는 것을 볼 수 있다.

설명에 따르면,

| Image Sensor Array | 656 x 488 개의 픽셀을 가지고, 실제 동작은 640 x 480 픽셀이 동작한다. |

| Timing Generator | 배열 조작과 프레임 생성을 담당한다. 내부 타이밍 신호 생성과 분배를 담당한다. 프레임률 타이밍 자동 노출 조작(Automatic Exposure Control) 외부 타이밍 (VSYNC, HREF(HSYNC), PCLK) 출력 |

| Analog Signal Processor | Automatic Gain Control Automatic White Balance 주로 카메라 동작과 관련됨 |

| A/D Converter | Analog Signal Processing block 이후, 베이어 패턴이 10-bit analog-to-digital Converter 로 들어감(G, BR channel) * 베이어 패턴 참고 https://darkpgmr.tistory.com/97 이 A/D 컨버터는 12Mhz 속도로 움직이고, Pixel rate 와 완전히 동기화됨. 다른 기능들도 있는데 생략(카메라 기능에 대한 것들) |

| Test Pattern Generator | 말 그대로 테스트용 |

| Digital Signal Processor | 이 블럭은 raw data 에서 RGB 로의 보간(interpolation) 과 일부 화질 제어를 담당함. 가장자리 강화 / RGB to YUV or YCbCr 로 변화 / 10비트 데이터를 8비트로 전환 등등 |

| Image Scaler | 이미지 외부 출력 전 모든 필요한 모든 출력 및 데이터 포맷 제어 이 블록은 VGA에서 CIF, CIF보다 작은 대부분의 크기로 YUV/RGB 출력을 변환한다. |

| Digital Video Port | 레지스터 비트 COM2[1:0] 에 관련.. 일단 넘어감 |

| SCCB interface | 처음에 한 내용 |

| LED and Strobe Flash Control Output |

외부 플래시, LED 관련 |

Pin 설정

하나의 Master, 하나의 Slave만 가지기 때문에 2-Wire communication 발생

가지고 있는 모듈보다 핀의 개수가 많은 것을 확인 가능하다.

OV7670만이 아닌 OV7171도 포함하는 datasheet 라서 그런 건가 생각한다.

전력이나 다른 것들은 따로 제어하기 힘드므로 타이밍을 본다.

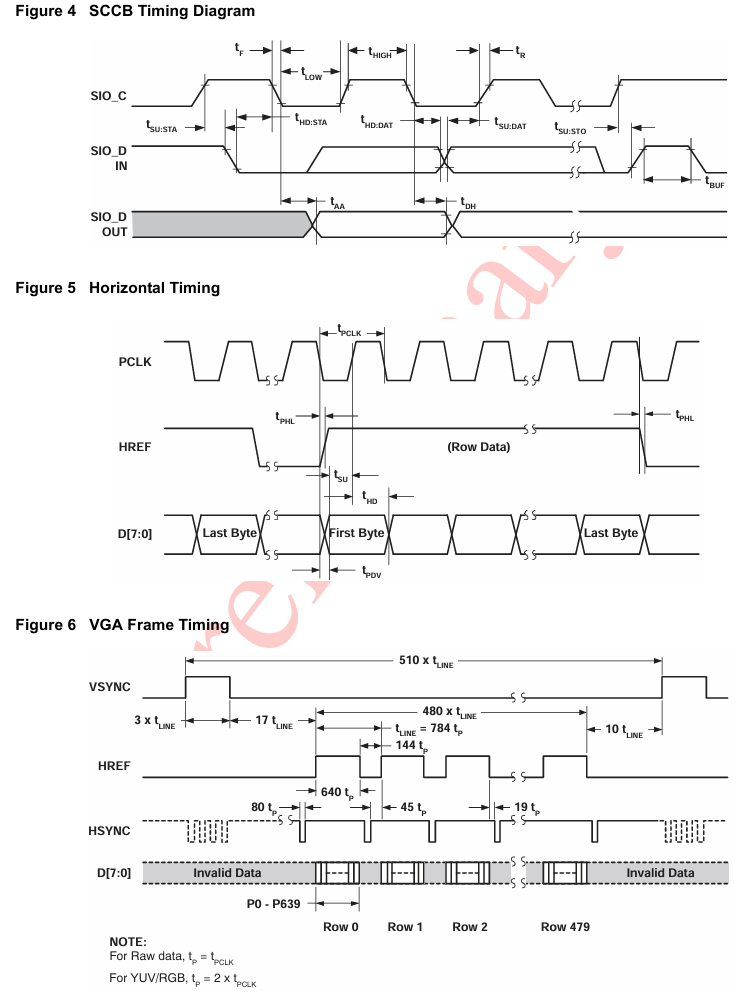

그림 4~10을 참고하라고 하니 한 번 본다.

7~10 까지는 VGA가 아닌 다른 해상도일 때 HREF(HSYNC) 판단을 하는 것 같다.

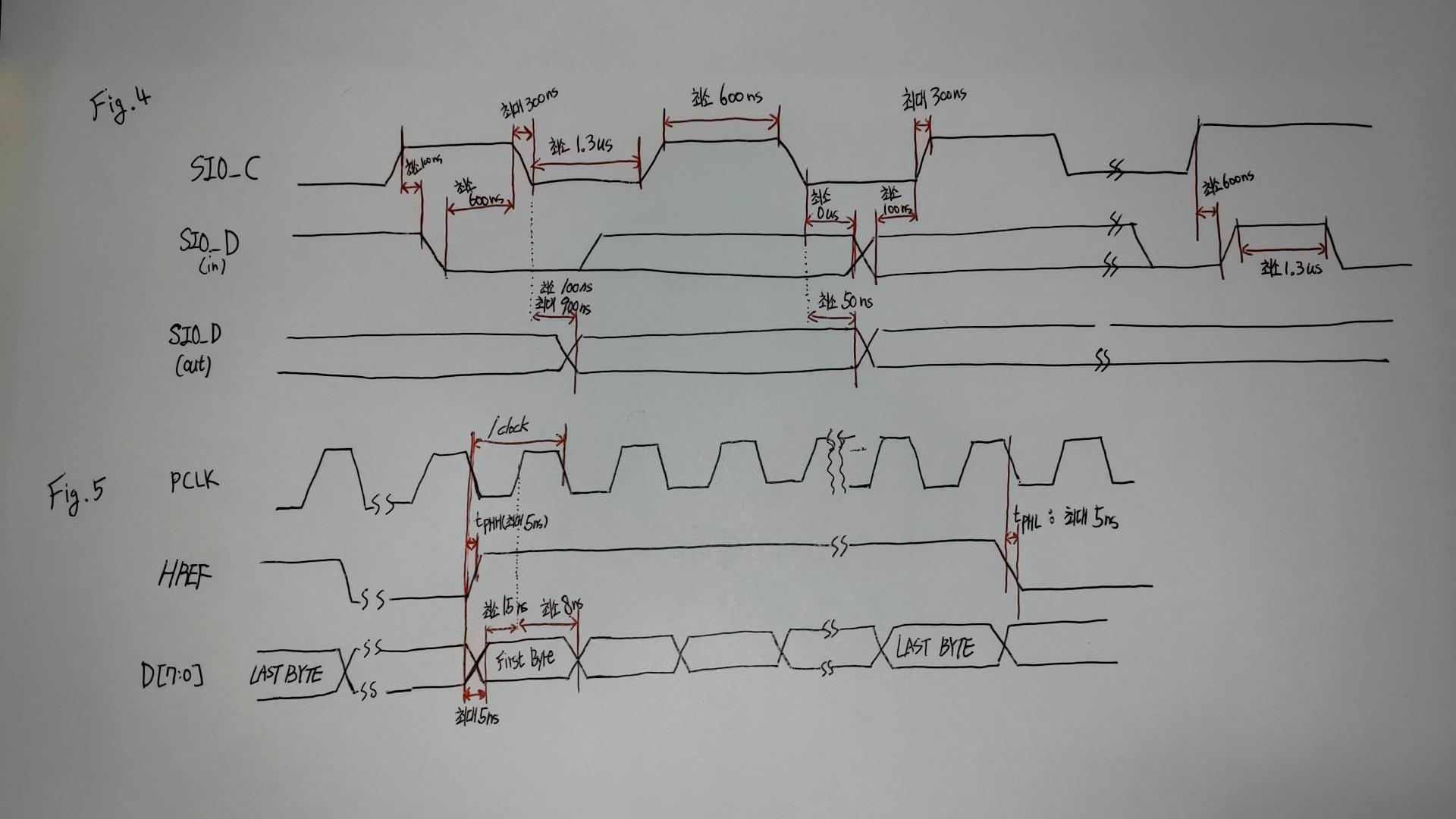

그림 4로 돌아와 보자.

시간을 넣으면 다음과 같다.

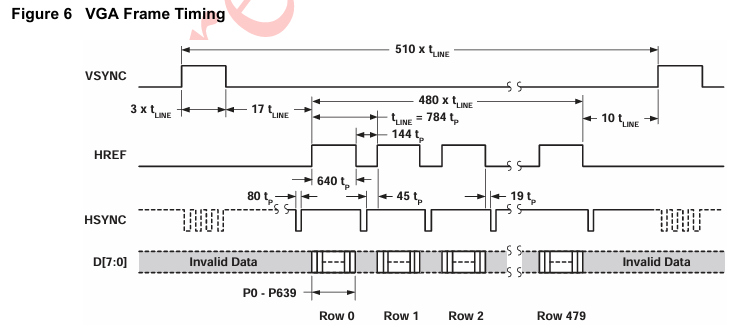

Fig.6 의 경우, VGA(640*480) 으로 출력하기 위한 코드이다.

한 픽셀에 8비트 데이터가 계속 전달되는 식으로 동작한다.

아래 Note 를 보면,

Raw Data : t_P = t_PCLK

YUV/RGB : t_P = 2 * t_PCLK

라고 적혀있는 것을 볼 수 있다.

왜일까?

Fig. 11을 보자.

RGB565 output timing diagram 이다.

두 개의 바이트가 한 쌍을 이루는 것을 알 수 있다.

그리고 다른 색상보다 Green 이 1비트 더 많이 표현한다.

사람의 눈은 초록색을 더 민감하게 인지하기 때문에 그렇다.. 라고 한다.

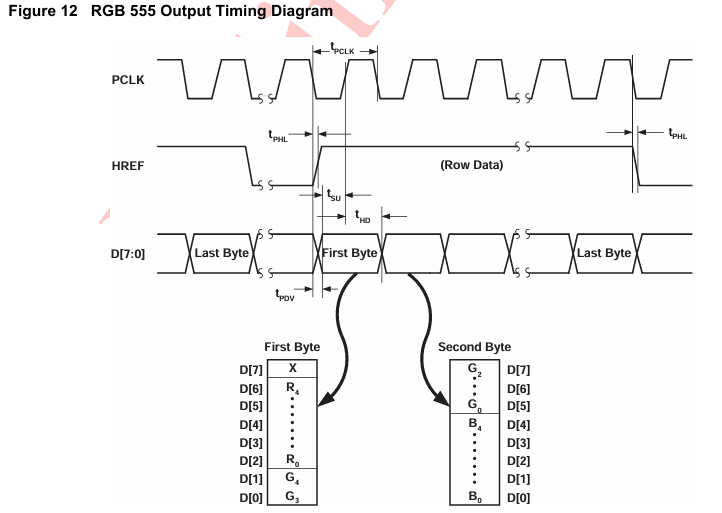

다음 그림인 Fig. 12 를 보자.

RGB 555 output timing diagram 이다.

R, G, B 모두 5비트로 맞춰주기 위해 처음 바이트의 MSB는 Don't care 상태이다.

다시 Fig. 6 으로 돌아가도록 하자.

단순하게 생각해 보자.

VGA(640 * 480) 는 다음의 타이밍도를 따른다.

VGA Signal 640 x 480 @ 60 Hz Industry standard timing (tinyvga.com)

VGA Signal 640 x 480 @ 60 Hz Industry standard timing

VGA Signal 640 x 480 @ 60 Hz Industry standard timing General timing Screen refresh rate60 HzVertical refresh31.46875 kHzPixel freq.25.175 MHz Horizontal timing (line) Polarity of horizontal sync pulse is negative. Scanline partPixelsTime [µs]Visible area

tinyvga.com

상세하게 보면, 좀 다르긴 하다.

그래도 Front porch, sync pulse, back porch 등이 존재해서 기존 보이는 화면보다 뭐가 더 추가되었구나 하는 것을 알면 될 것 같다.

OV7670에서 제시하는 VGA 는 다음과 같다.

Col 784 Lines

Row 510 Lines

Col_active 640 Lines

Row_active 480 Lines

나머지는 제어 관련이라고 생각하면 좋을 것 같다.

아까 손으로 직접 그린 그림에 t_P가 1 clock 이라고 적혀있는데,

이는 1 pixel clock이다.

VGA ref 를 참고하면 동작에 25 Mhz 가 나온다.

그런데, 이는 60Hz 즉 60FPS 상에서 25Mhz가 필요하다.

카메라는 30FPS 촬영을 한다.

대충 생각해 봐도 손실이 있을 것 같은 느낌이 든다.(Raw 데이터의 경우)

일단 1초에 30frame 을 나타내려면 대략 33ms 당 1 frame 을 뽑아내야 한다.

그러기 위해서는 33ms 안에 784 * 510 = 399,840 pixels 에 대해 처리가 끝나야 된다는 소리이다.

t_P (pixel clock) 를 25Mhz 라고 가정해 보자. 그럼 1 clock 에 40ns 가 소요된다. (Raw 데이터의 경우)

1번의 row 가 끝나기 위해서는 784번의 clock이 필요하고, 510번 반복되어야 한다.

결국 399,840 픽셀에 걸리는 처리 시간과 동일해진다.

40ns * 399,840 = 15,993,600 ns = 약 16ms

이 시간은 60fps 를 뽑아낼 수 있는 시간대이다.(Raw data의 경우)

YUV/RGB 데이터에 대해서는 어떨까

t_P = 2 * t_PCLK 이다.

가로 사이즈가 2배로 걸리고 세로는 그대로이다.

그러면 1번의 row가 끝나기 위해서는 1568번의 clock이 필요하고, 510번 반복되어야 한다.

= 799,680 * 40ns = 31,987,200 약 32ms

거의 30 프레임을 나타낼 수 있게 된다.

추후 작성 예정

'Verilog' 카테고리의 다른 글

| [Verilog] maxpool2d w. line buffer (0) | 2024.10.31 |

|---|---|

| [Verilog] Conv2d w. line buffer (0) | 2024.10.30 |

| [Verilog] OV7670 카메라 모듈과 FPGA 통신 (0) | 2024.09.09 |

| [Verilog] OV7670 - more2 (0) | 2024.05.28 |

| [Verilog] SCCB & OV7670 - more1 (0) | 2024.05.28 |