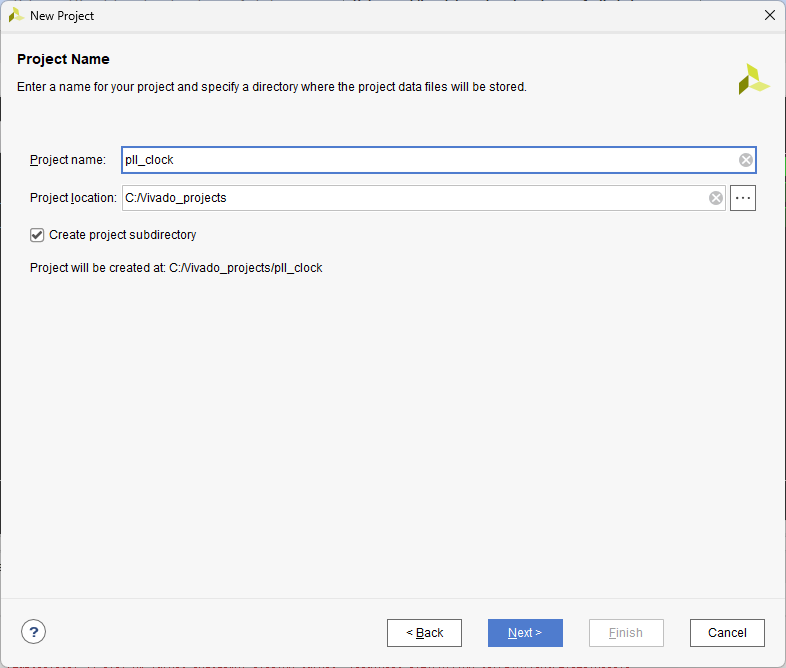

프로젝트 생성부터 시작한다.

Project name : pll_clock

Project type : RTL

Source : X

프로젝트를 생성 후 pll_clock_top.v 파일을 생성해 준다.

코드는 다음과 같다.

module pll_clock_top(

input i_Clk,

input i_Rst,

output reg [3:0] o_LED

);

parameter CLOCK_FREQ = 1_000_000_00;

parameter COUNTER_MAX_CNT=CLOCK_FREQ/2 - 1;

reg [31:0] cnt;

reg [1:0] led_on_number;

wire clk_out1;

clk_wiz_0 clk_wiz_0_inst(

.clk_out1(clk_out1),

.resetn(i_Rst),

.locked(),

.clk_in1(i_Clk)

);

always@(posedge clk_out1, negedge i_Rst) begin

if(!i_Rst) begin

cnt <= 32'd0;

led_on_number <= 2'd0;

end else begin

cnt <= cnt + 1'b1;

if(cnt == COUNTER_MAX_CNT) begin

cnt <= 32'd0;

led_on_number <= led_on_number + 1'b1;

end

end

end

always@(led_on_number) begin

case(led_on_number)

0: o_LED <= 4'b0001;

1: o_LED <= 4'b0010;

2: o_LED <= 4'b0100;

3: o_LED <= 4'b1000;

default: o_LED <= 4'b1111;

endcase

end

endmodule

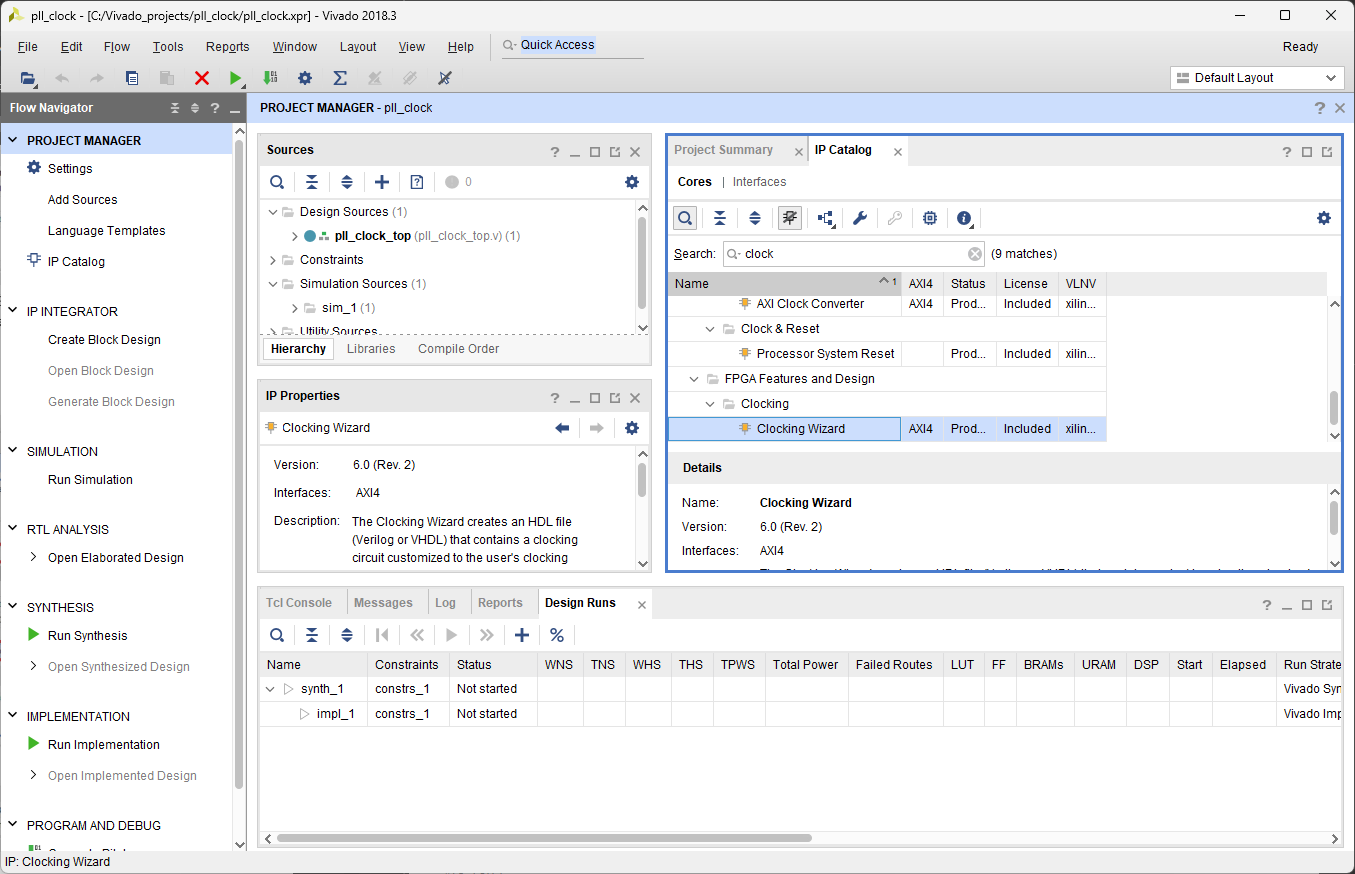

Project manager > IP catalog 를 클릭 해 준다.

IP(Intellectual Property) 는 재사용 가능한 블럭들을 지칭한다. 근데 이 블럭들은 기능을 가지고 있는

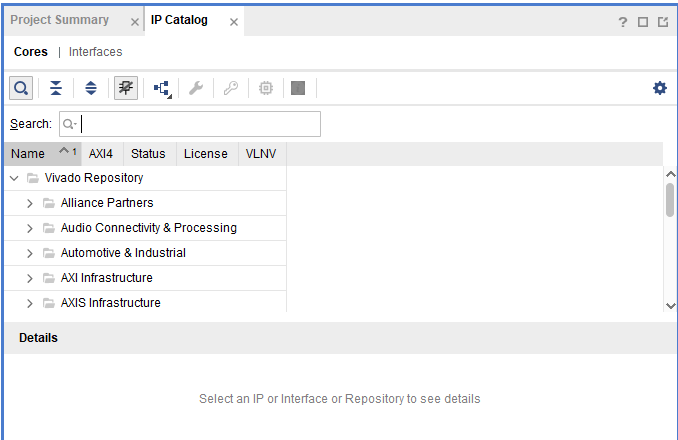

그러면 다음과 같은 창이 나온다.

Search : clock

아래에 있는 FPGA Features and Design > Clocking > Clocking Wizard 를 더블클릭 해 준다.

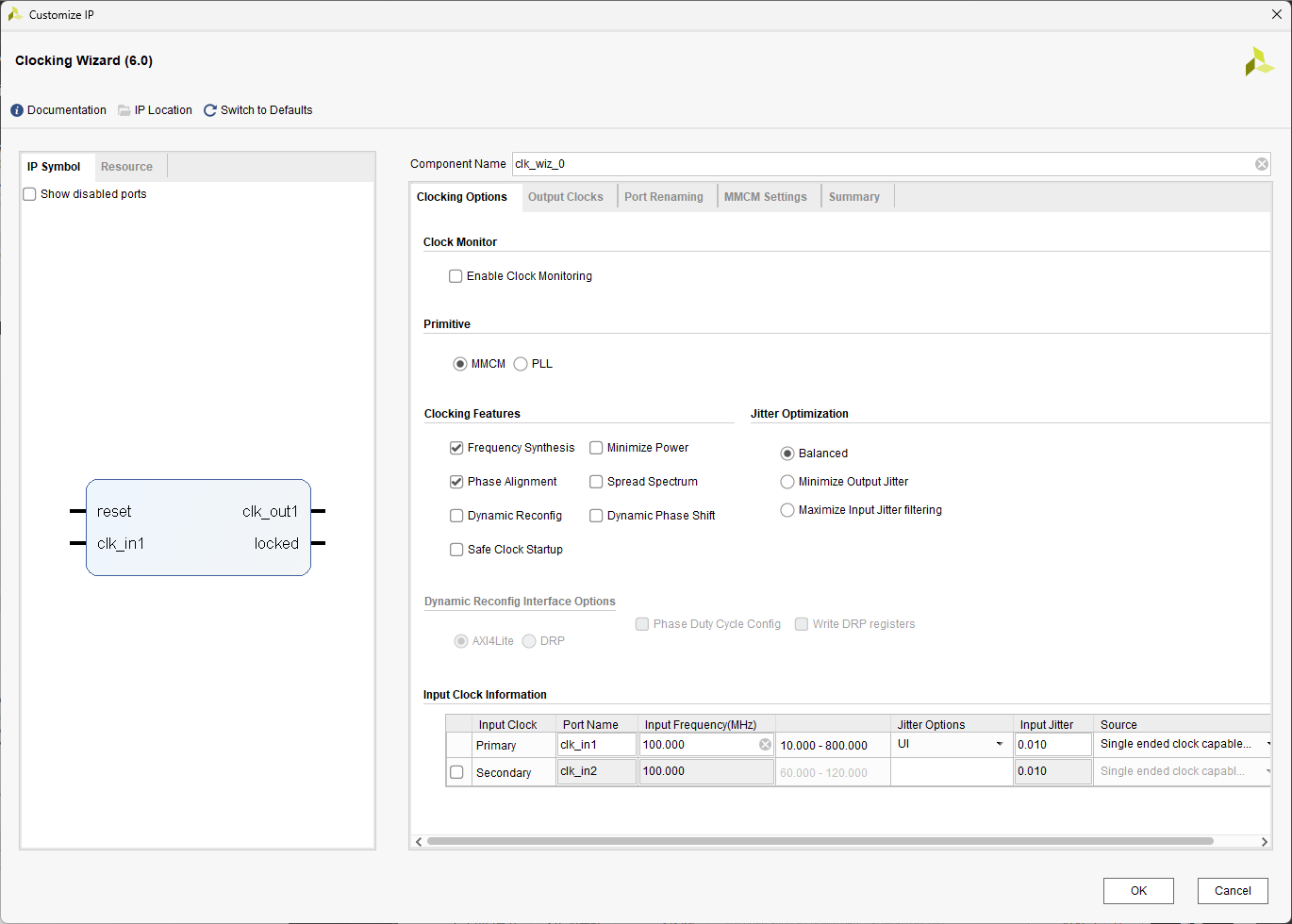

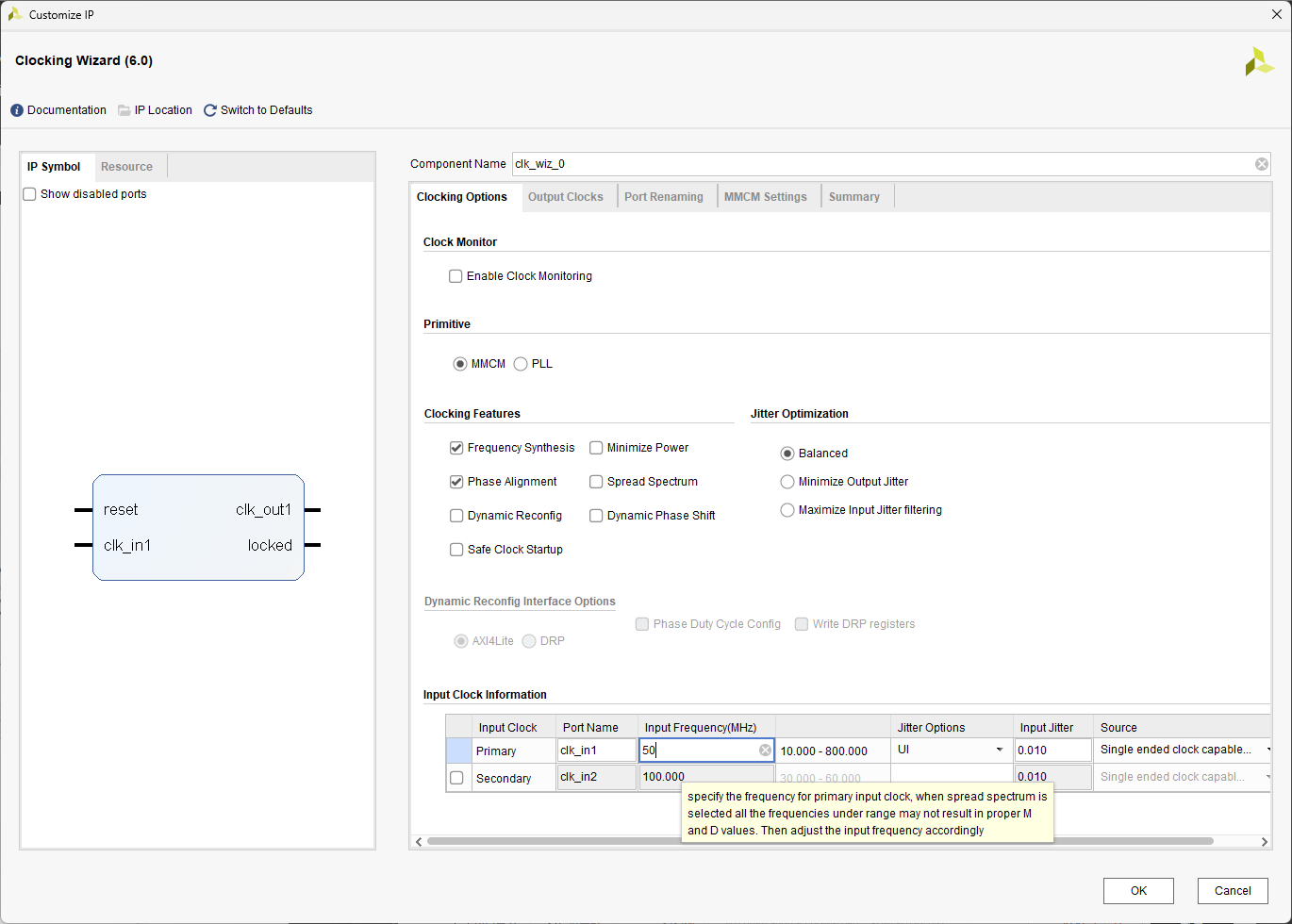

다음과 같은 IP 생성창이 나온다.

Input Frequency 를 50Mhz 로 조정해 준다.

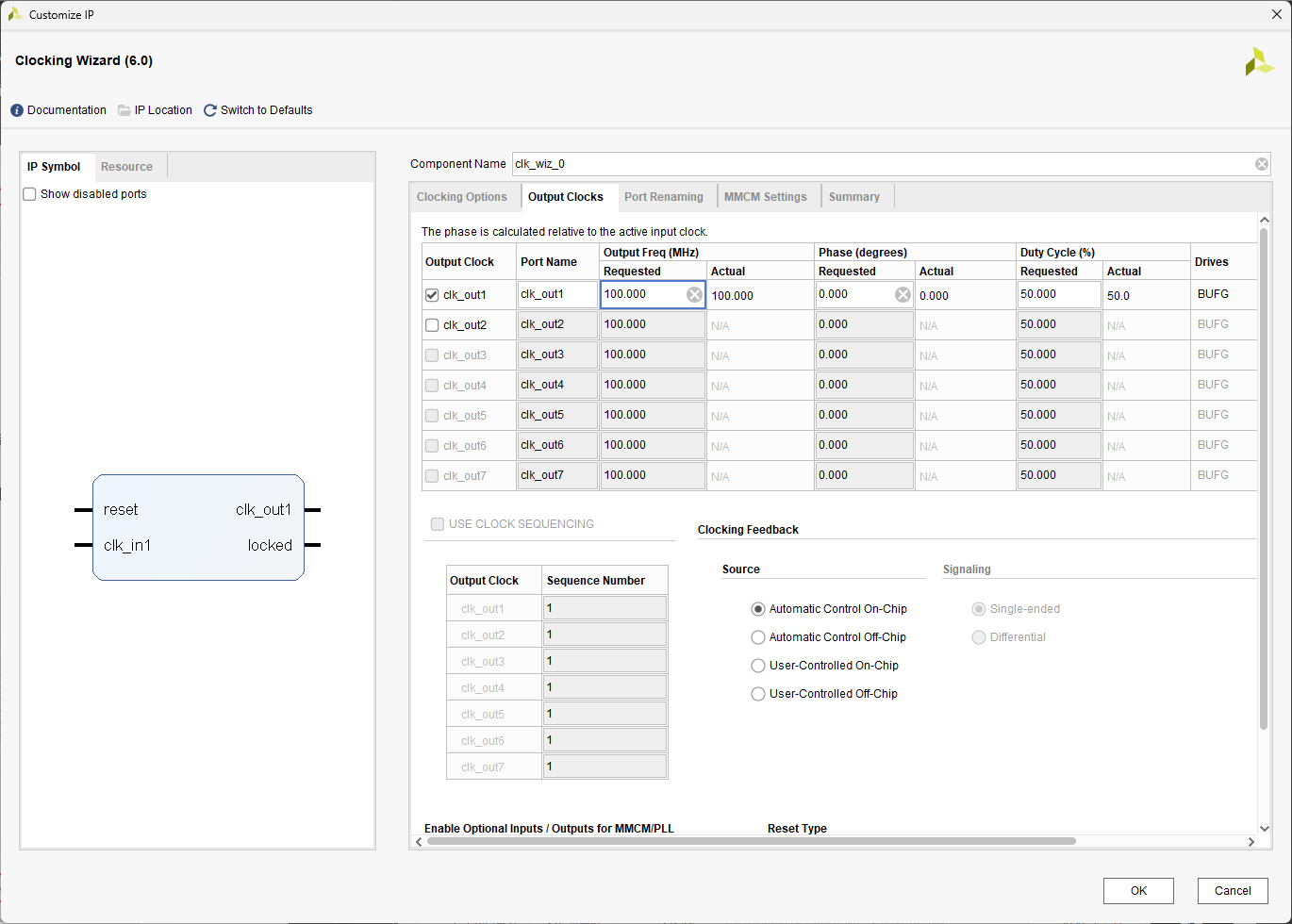

위의 Output Clocks 탭을 클릭하고 clk_out1이 100Mhz인지 확인한다.

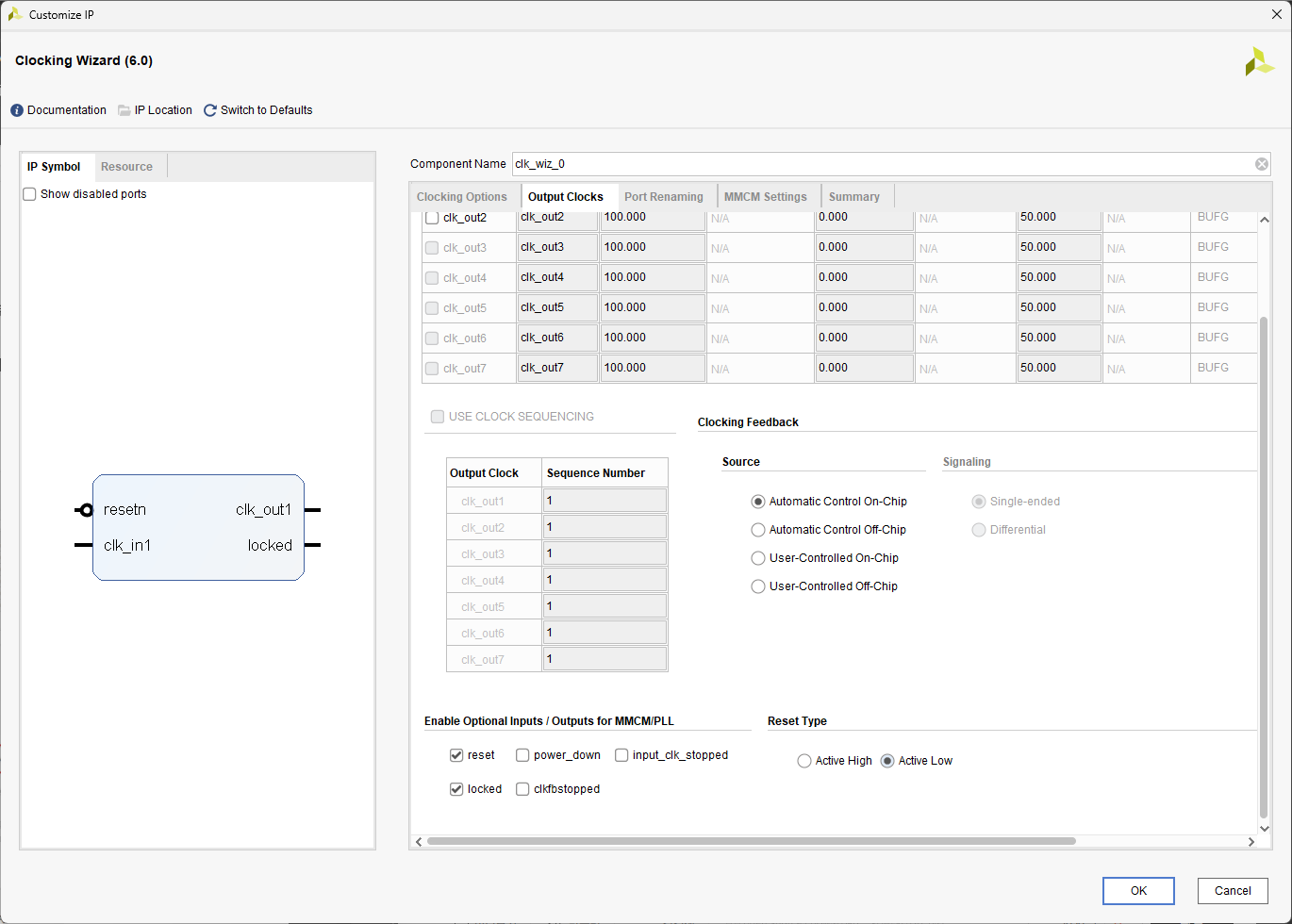

이 창에서 휠 다운을 해서 Reset Type > Negetive 로 돌려준다.(Active low)

OK 를 눌러 생성한다.

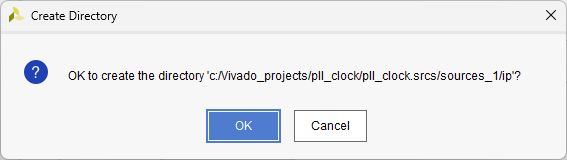

OK > 다음과 같은 창이 나온다.

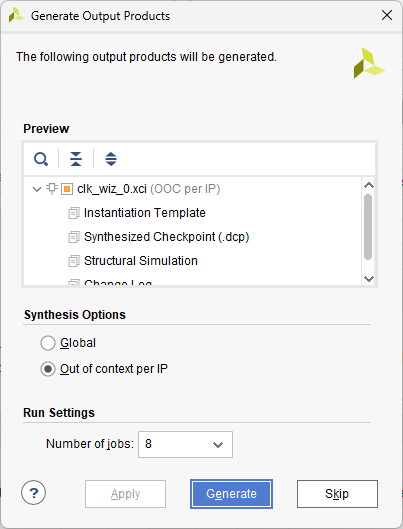

이 정보가 생성이 된다고 알려주는데 그냥 generate 시킨다.

생성을 다하면 다음과 같은 창이 나오고 OK 눌러준다.

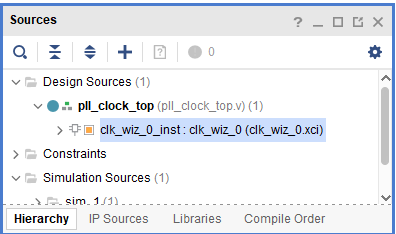

그럼 소스에 IP가 추가되어 있는 것을 볼 수 있다.

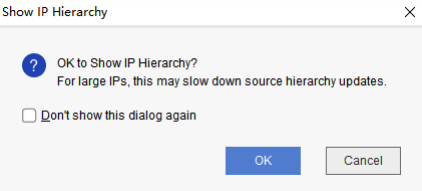

다음 사진과 같이 빨간 원을 친 부분을 누르면

이런 창이 뜨는데, OK를 눌러준다. 그러면 아래에 clk_wiz_0이 생기는걸 볼 수 있다(위 사진과 같음)

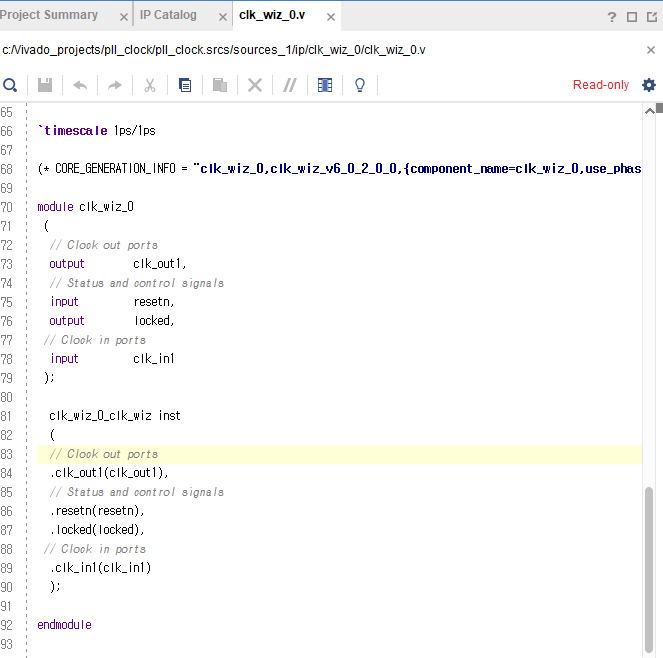

생성된 clk_wiz_0.v 파일을 열어본다.

자동 생성된 clk_wiz_0 모듈을 볼 수 있다.

이 모듈은 submodule 로 clk_wiz_0_clk_wiz 를 받는다.

그리고 우리가 설정한 대로 input 50Mhz clock 을 output 100Mhz clock 으로 늘려주는 역할을 한다.

모듈을 상세하게 더 알아보고 싶으면 submodule 을 클릭해 보면 된다.

'ZYNQ_MINI' 카테고리의 다른 글

| [ZYNQ MINI] Linaro LINUX 사용해 보기 + HDMI 세팅 - [2] (0) | 2024.04.29 |

|---|---|

| [ZYNQ MINI] Linaro LINUX 사용해 보기 + HDMI 세팅 - [1] (0) | 2024.04.19 |

| [ZYNQ MINI] PWM 예제, Simulation 써 보기 (0) | 2024.04.12 |

| [ZYNQ MINI] 보드로 petalinux 돌려보기 - [3] (0) | 2024.04.03 |

| [ZYNQ MINI] 보드로 petalinux 돌려보기 - [2] (0) | 2024.04.01 |